# **VIPA System 200V**

**FM | Manual** HB97E\_FM | RE\_250-1BA00 | Rev. 13/02 January 2013

#### Copyright © VIPA GmbH. All Rights Reserved.

This document contains proprietary information of VIPA and is not to be disclosed or used except in accordance with applicable agreements.

This material is protected by the copyright laws. It may not be reproduced, distributed, or altered in any fashion by any entity (either internal or external to VIPA), except in accordance with applicable agreements, contracts or licensing, without the express written consent of VIPA and the business management owner of the material.

For permission to reproduce or distribute, please contact: VIPA, Gesellschaft für Visualisierung und Prozessautomatisierung mbH Ohmstraße 4, D-91074 Herzogenaurach, Germany Tel.: +49 (91 32) 744 -0 Fax.: +49 9132 744 1864 EMail: info@vipa.de http://www.vipa.com

#### Note

Every effort has been made to ensure that the information contained in this document was complete and accurate at the time of publishing. Nevertheless, the authors retain the right to modify the information. This customer document describes all the hardware units and functions known at the present time. Descriptions may be included for units which are not present at the customer site. The exact scope of delivery is described in the respective purchase contract.

#### **CE Conformity Declaration**

Hereby, VIPA GmbH declares that the products and systems are in compliance with the essential requirements and other relevant provisions.

Conformity is indicated by the CE marking affixed to the product.

#### **Conformity Information**

For more information regarding CE marking and Declaration of Conformity (DoC), please contact your local VIPA customer service organization.

#### Trademarks

VIPA, SLIO, System 100V, System 200V, System 300V, System 300S, System 400V, System 500S and Commander Compact are registered trademarks of VIPA Gesellschaft für Visualisierung und Prozessautomatisierung mbH.

SPEED7 is a registered trademark of profichip GmbH.

SIMATIC, STEP, SINEC, TIA Portal, S7-300 and S7-400 are registered trademarks of Siemens AG.

Microsoft und Windows are registered trademarks of Microsoft Inc., USA.

Portable Document Format (PDF) and Postscript are registered trademarks of Adobe Systems, Inc.

All other trademarks, logos and service or product marks specified herein are owned by their respective companies.

#### Information product support

Contact your local VIPA Customer Service Organization representative if you wish to report errors or questions regarding the contents of this document. If you are unable to locate a customer service center, contact VIPA as follows:

VIPA GmbH, Ohmstraße 4, 91074 Herzogenaurach, Germany

Telefax:+49 9132 744 1204 EMail: documentation@vipa.de

#### **Technical support**

Contact your local VIPA Customer Service Organization representative if you encounter problems with the product or have questions regarding the product. If you are unable to locate a customer service center, contact VIPA as follows:

VIPA GmbH, Ohmstraße 4, 91074 Herzogenaurach, Germany

Telephone: +49 9132 744 1150 (Hotline) EMail: support@vipa.de

# Contents

| About this manual                        |      |  |  |  |

|------------------------------------------|------|--|--|--|

| Safety information                       |      |  |  |  |

| Chapter 1 Basics and Assembly            |      |  |  |  |

| Safety Information for Users             |      |  |  |  |

| System conception                        |      |  |  |  |

| Dimensions                               |      |  |  |  |

| Installation                             |      |  |  |  |

| Demounting and module exchange           |      |  |  |  |

| Wiring                                   |      |  |  |  |

| Installation guidelines                  | 1-14 |  |  |  |

| General data                             |      |  |  |  |

| Chapter 2 Hardware description           |      |  |  |  |

| Properties                               |      |  |  |  |

| Structure                                |      |  |  |  |

| Technical data                           |      |  |  |  |

| Chapter 3 Deployment                     |      |  |  |  |

| Data input / output                      |      |  |  |  |

| Summary of counter modes and interfacing |      |  |  |  |

| Counter modes                            |      |  |  |  |

# About this manual

This manual describes the System 200V Counter module FM 250 from VIPA. Here you may find every information for commissioning and operation.

#### Overview Chapter 1: Basics and Assembly

The focus of this chapter is on the introduction of the VIPA System 200V. Here you will find the information required to assemble and wire a controller system consisting of System 200V components.

Besides the dimensions the general technical data of System 200V will be found.

#### Chapter 2: Hardware description

Here the hardware components of the FM 250-1BA00 are described. The technical data are at the end of the chapter.

#### Chapter 3: Deployment

This chapter provides information to the configuration and the various counter modes of the Counter module FM 250 are described.

Objective and contents

This manual describes the System 200V Counter module FM 250-1BA00 from VIPA. It contains a description of the construction, project implementation and usage.

This manual is part of the documentation package with order number HB97E\_FM and relevant for:

Product

Order number

HW

| Product |                | HW |

|---------|----------------|----|

| FM 250  | VIPA 250-1BA00 | 01 |

Target audienceThe manual is targeted at users who have a background in automation<br/>technology.

Structure of the<br/>manualThe manual consists of chapters. Every chapter provides a self-contained<br/>description of a specific topic.

- Guide to the<br/>documentThe following guides are available in the manual:<br/>• an overall table of contents at the beginning of the manual

- an overview of the topics for every chapter

Availability The manual is available in:

- printed form, on paper

- in electronic form as PDF-file (Adobe Acrobat Reader)

IconsImportant passages in the text are highlighted by following icons and<br/>headings:

**Danger!** Immediate or likely danger. Personal injury is possible.

Attention! Damages to property is likely if these warnings are not heeded.

**Note!** Supplementary information and useful tips.

# Safety information

Applications conforming with specifications The FM 250 is constructed and produced for:

- all VIPA System 200V components

- communication and process control

- general control and automation applications

- industrial applications

- operation within the environmental conditions specified in the technical data

- installation into a cubicle

#### Danger!

This device is not certified for applications in

• in explosive environments (EX-zone)

Documentation

The manual must be available to all personnel in the

- project design department

- installation department

- commissioning

- operation

# The following conditions must be met before using or commissioning the components described in this manual:

- Hardware modifications to the process control system should only be carried out when the system has been disconnected from power!

- Installation and hardware modification only by properly trained personnel.

- The national rules and regulations of the respective country must be satisfied (installation, safety, EMC ...)

Disposal

National rules and regulations apply to the disposal of the unit!

# Chapter 1 Basics and Assembly

OverviewThe focus of this chapter is on the introduction of the VIPA System 200V.<br/>Here you will find the information required to assemble and wire a controller<br/>system consisting of System 200V components.<br/>Besides the dimensions the general technical data of System 200V will be<br/>found.

| Contents | Торіс                          | Page |

|----------|--------------------------------|------|

|          | Chapter 1 Basics and Assembly  | 1-1  |

|          | Safety Information for Users   |      |

|          | System conception              |      |

|          | Dimensions                     |      |

|          | Installation                   |      |

|          | Demounting and module exchange |      |

|          | Wiring                         |      |

|          | Installation guidelines        |      |

|          | General data                   | 1-17 |

## Safety Information for Users

Handling of electrostatic sensitive modules VIPA modules make use of highly integrated components in MOS-Technology. These components are extremely sensitive to over-voltages that can occur during electrostatic discharges.

The following symbol is attached to modules that can be destroyed by electrostatic discharges.

The Symbol is located on the module, the module rack or on packing material and it indicates the presence of electrostatic sensitive equipment.

It is possible that electrostatic sensitive equipment is destroyed by energies and voltages that are far less than the human threshold of perception. These voltages can occur where persons do not discharge themselves before handling electrostatic sensitive modules and they can damage components thereby, causing the module to become inoperable or unusable.

Modules that have been damaged by electrostatic discharges can fail after a temperature change, mechanical shock or changes in the electrical load.

Only the consequent implementation of protection devices and meticulous attention to the applicable rules and regulations for handling the respective equipment can prevent failures of electrostatic sensitive modules.

Modules must be shipped in the original packing material.

Shipping of electrostatic sensitive modules

Measurements and alterations on electrostatic sensitive modules When you are conducting measurements on electrostatic sensitive modules you should take the following precautions:

- Floating instruments must be discharged before use.

- Instruments must be grounded.

Modifying electrostatic sensitive modules you should only use soldering irons with grounded tips.

#### Attention!

Personnel and instruments should be grounded when working on electrostatic sensitive modules.

# System conception

#### Overview

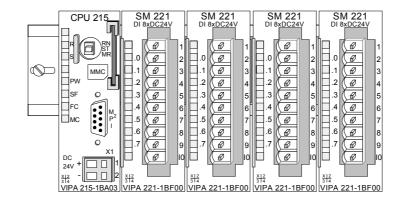

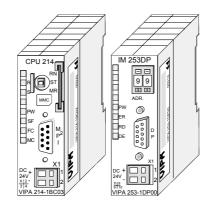

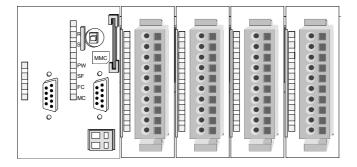

The System 200V is a modular automation system for assembly on a 35mm profile rail. By means of the peripheral modules with 4, 8 and 16 channels this system may properly be adapted matching to your automation tasks.

#### Components

The System 200V consists of the following components:

- Head modules like CPU and bus coupler

- Periphery modules like I/O, function und communication modules

- Power supplies

- Extension modules

#### Head modules

With a head module CPU respectively bus interface and DC 24V power supply are integrated to one casing.

Via the integrated power supply the CPU respectively bus interface is power supplied as well as the electronic of the connected periphery modules.

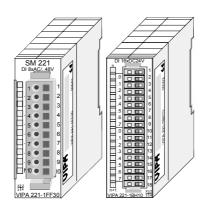

#### **Periphery modules**

The modules are direct installed on a 35mm profile rail and connected to the head module by a bus connector, which was mounted on the profile rail before.

Most of the periphery modules are equipped with a 10pin respectively 18pin connector. This connector provides the electrical interface for the signaling and supplies lines of the modules.

#### **Power supplies**

Expansion modules

With the System 200V the DC 24V power supply can take place either externally or via a particularly for this developed power supply.

The power supply may be mounted on the profile rail together with the System 200V modules. It has no connector to the back-plane bus.

The expansion modules are complementary modules providing 2- or 3wire connection facilities.

The modules are not connected to the backplane bus.

Structure/ dimensions

- Profile rail 35mm

- Dimensions of the basic enclosure: 1tier width: (HxWxD) in mm: 76x25.4x74 in inches: 3x1x3 2tier width: (HxWxD) in mm: 76x50.8x74 in inches: 3x2x3

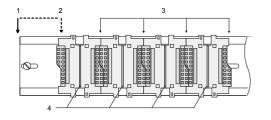

#### Installation

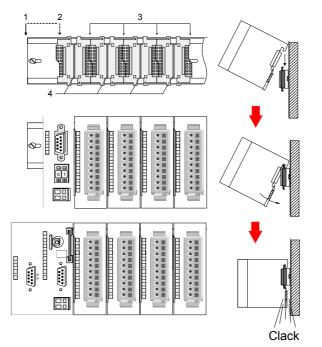

Please note that you can only install head modules, like the CPU, the PC and couplers at slot 1 or 1 and 2 (for double width modules).

| [1] | Head module      |

|-----|------------------|

|     | (double width)   |

| [2] | Head module      |

|     | (single width)   |

| [3] | Periphery module |

| [4] | Guide rails      |

|     |                  |

#### Note

Information about the max. number of pluggable modules and the max. current at the backplane bus can be found in the "Technical Data" of the according head module.

Please install modules with a high current consumption directly beside the head module.

0

60 mm

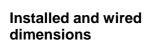

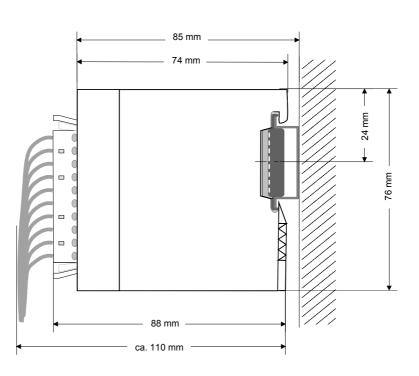

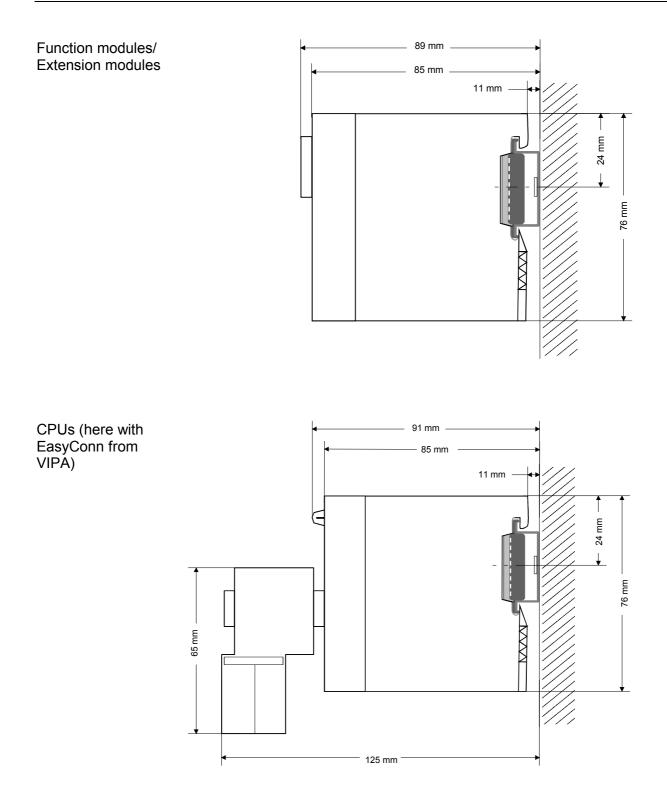

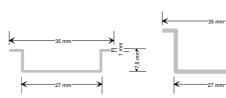

# Dimensions

| Dimensions<br>Basic enclosure | 1tier width (HxWxD) in mm: 76 x 25.4 x 74<br>2tier width (HxWxD) in mm: 76 x 50.8 x 74 |  |

|-------------------------------|----------------------------------------------------------------------------------------|--|

| Installation<br>dimensions    |                                                                                        |  |

In- / Output modules

# Installation

**General** The modules are each installed on a 35mm profile rail and connected via a bus connector. Before installing the module the bus connector is to be placed on the profile rail before.

Profile rail

For installation the following 35mm profile rails may be used:

| Order number | Label             | Description                |

|--------------|-------------------|----------------------------|

| 290-1AF00    | 35mm profile rail | Length 2000mm, height 15mm |

| 290-1AF30    | 35mm profile rail | Length 530mm, height 15mm  |

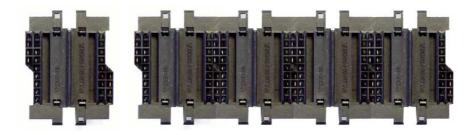

**Bus connector** System 200V modules communicate via a backplane bus connector. The backplane bus connector is isolated and available from VIPA in of 1-, 2-, 4- or 8tier width.

The following figure shows a 1tier connector and a 4tier connector bus:

The bus connector is to be placed on the profile rail until it clips in its place and the bus connections look out from the profile rail.

| Order number | Label         | Description |

|--------------|---------------|-------------|

| 290-0AA10    | Bus connector | 1tier       |

| 290-0AA20    | Bus connector | 2tier       |

| 290-0AA40    | Bus connector | 4tier       |

| 290-0AA80    | Bus connector | 8tier -     |

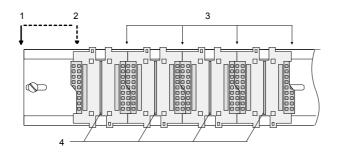

# Installation on a<br/>profile railThe following figure shows the installation of a 4tier width bus connector in<br/>a profile rail and the slots for the modules.

The different slots are defined by guide rails.

- [1] Head module

- (double width)

- [2] Head module

- (single width)

- [3] Peripheral module

- [4] Guide rails

Assembly regarding the current consumption

- Use bus connectors as long as possible.

- Sort the modules with a high current consumption right beside the head module. In the service area of www.vipa.com a list of current consumption of every System 200V module can be found.

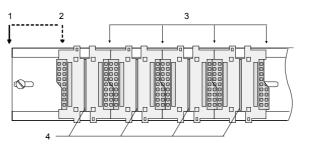

# Assembly possibilities

hoizontal assembly

lying assembly

| - | _ | _ | _                | _        | <br>     | _ | _        | _ | _ | _ |       |  |         |

|---|---|---|------------------|----------|----------|---|----------|---|---|---|-------|--|---------|

|   |   |   | E                |          |          |   |          | F | E |   |       |  |         |

|   |   |   |                  |          |          |   |          |   |   |   |       |  |         |

|   |   |   | $\left  \right $ | $\vdash$ | $\vdash$ |   | $\vdash$ | ⊢ |   | - | +     |  | <u></u> |

|   |   |   | F                |          | F        |   | F        | F |   |   | <br>F |  | 0       |

|   |   |   | F                |          | F        |   |          | F |   |   | F     |  |         |

|   |   |   |                  |          |          |   |          |   |   |   |       |  |         |

|   |   |   |                  |          |          |   |          |   |   |   |       |  |         |

vertical assembly

Ŷ

Please regard the allowed environmental temperatures:

- horizontal assembly:

- vertical assembly: from 0 to 40°C

- lying assembly:

from 0 to 40°C

from 0 to 60°C

The horizontal assembly always starts at the left side with a head module, then you install the peripheral modules beside to the right.

You may install up to 32 peripheral modules.

#### Please follow these rules during the assembly!

- Turn off the power supply before you install or remove any modules!

- Make sure that a clearance of at least 60mm exists above and 80mm below the middle of the profile rail.

- Every row must be completed from left to right and it has to start with a head module.

- [1] Head module (double width)

- [2] Head module (single width)

- [3] Peripheral modules

- [4] Guide rails

- Modules are to be installed side by side. Gaps are not permitted between the modules since this would interrupt the backplane bus.

- A module is only installed properly and connected electrically when it has clicked into place with an audible click.

- Slots after the last module may remain unoccupied.

#### Note!

Information about the max. number of pluggable modules and the max. current at the backplane bus can be found in the "Technical Data" of the according head module.

Please install modules with a high current consumption directly beside the head module.

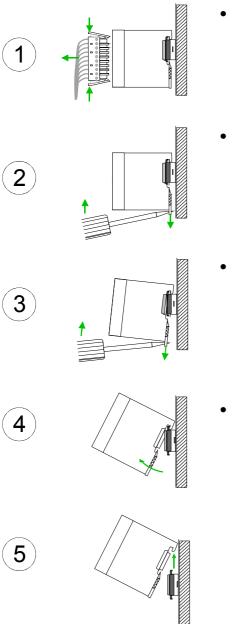

# Assembly procedure

• Install the profile rail. Make sure that a clearance of at least 60mm exists above and 80mm below the middle of the profile rail.

- Press the bus connector into the profile rail until it clips securely into place and the bus-connectors look out from the profile rail. This provides the basis for the installation of your modules.

- Start at the outer left location with the installation of your head module and install the peripheral modules to the right of this.

- [1] Head module (double width)

- [2] Head module (single width)

- [3] Peripheral module

- [4] Guide rails

- Insert the module that you are installing into the profile rail at an angle of 45 degrees from the top and rotate the module into place until it clicks into the profile rail with an audible click. The proper connection to the backplane bus can only be guaranteed when the module has properly clicked into place.

#### Attention!

Power must be turned off before modules are installed or removed!

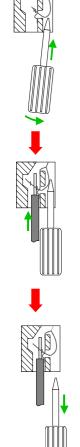

# Demounting and module exchange

- Remove if exists the wiring to the module, by pressing both locking lever on the connector and pulling the connector.

- The casing of the module has a spring loaded clip at the bottom by which the module can be removed.

- The clip is unlocked by pressing the screwdriver in an upward direction.

- Withdraw the module with a slight rotation to the top.

#### Attention!

Power must be turned off before modules are installed or removed!

Please regard that the backplane bus is interrupted at the point where the module was removed!

# Wiring

Overview

Most peripheral modules are equipped with a 10pole or a 18pole connector. This connector provides the electrical interface for the signaling and supply lines of the modules.

The modules carry spring-clip connectors for interconnections and wiring.

The spring-clip connector technology simplifies the wiring requirements for signaling and power cables.

In contrast to screw terminal connections, spring-clip wiring is vibration proof. The assignment of the terminals is contained in the description of the respective modules.

You may connect conductors with a diameter from  $0.08 \text{mm}^2$  up to  $2.5 \text{mm}^2$  (max.  $1.5 \text{mm}^2$  for 18pole connectors).

The following figure shows a module with a 10pole connector.

- [1] Locking lever

- [2] Pin no. at the module

- [3] Pin no. at the connector

- [4] Wiring port

- [5] Opening for screwdriver

#### Note!

The spring-clip is destroyed if you push the screwdriver into the wire port! Make sure that you only insert the screwdriver into the square hole of the connector!

#### Wiring procedure

Install the connector on the module until it locks with an audible click. For this purpose you press the two clips together as shown.

The connector is now in a permanent position and can easily be wired.

The following section shows the wiring procedure from top view.

- Insert a screwdriver at an angel into the square opening as shown.

- Press and hold the screwdriver in the opposite direction to open the contact spring.

- Insert the stripped end of the wire into the round opening. You can use wires with a diameter of 0.08mm<sup>2</sup> to 2.5mm<sup>2</sup> (1.5mm<sup>2</sup> for 18pole connectors).

• By removing the screwdriver the wire is connected safely with the plug connector via a spring.

#### Note!

Wire the power supply connections first followed by the signal cables (inputs and outputs).

# Installation guidelines

| General                            | The installation guidelines contain information about the interference free deployment of System 200V systems. There is the description of the ways, interference may occur in your control, how you can make sure the electromagnetic digestibility (EMC), and how you manage the isolation.                                                                                                                                                                                                                                        |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| What means EMC?                    | Electromagnetic digestibility (EMC) means the ability of an electrical device, to function error free in an electromagnetic environment without being interferenced res. without interferencing the environment.<br>All System 200V components are developed for the deployment in hard industrial environments and fulfill high demands on the EMC. Nevertheless you should project an EMC planning before installing the components and take conceivable interference causes into account.                                         |

| Possible<br>interference<br>causes | <ul> <li>Electromagnetic interferences may interfere your control via different ways:</li> <li>Fields <ul> <li>I/O signal conductors</li> <li>Bus system</li> <li>Current supply</li> <li>Protected earth conductor</li> </ul> </li> <li>Depending on the spreading medium (lead bound or lead free) and the distance to the interference cause, interferences to your control occur by means of different coupling mechanisms.</li> <li>One differs: <ul> <li>galvanic coupling</li> <li>capacitive coupling</li> </ul> </li> </ul> |

|                                    | inductive coupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                    | <ul> <li>radiant coupling</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

radiant coupling

**Basic rules for** In the most times it is enough to take care of some elementary rules to guarantee the EMC. Please regard the following basic rules when installing your PLC.

- Take care of a correct area-wide grounding of the inactive metal parts when installing your components.

- Install a central connection between the ground and the protected earth conductor system.

- Connect all inactive metal extensive and impedance-low.

- Please try not to use aluminum parts. Aluminum is easily oxidizing and is therefore less suitable for grounding.

- When cabling, take care of the correct line routing.

- Organize your cabling in line groups (high voltage, current supply, signal and data lines).

- Always lay your high voltage lines and signal res. data lines in separate channels or bundles.

- Route the signal and data lines as near as possible beside ground areas (e.g. suspension bars, metal rails, tin cabinet).

- Proof the correct fixing of the lead isolation.

- Data lines must be laid isolated.

- Analog lines must be laid isolated. When transmitting signals with small amplitudes the one sided laying of the isolation may be favorable.

- Lay the line isolation extensively on an isolation/protected earth conductor rail directly after the cabinet entry and fix the isolation with cable clamps.

- Make sure that the isolation/protected earth conductor rail is connected impedance-low with the cabinet.

- Use metallic or metalized plug cases for isolated data lines.

- In special use cases you should appoint special EMC actions.

- Wire all inductivities with erase links.

- Please consider luminescent lamps can influence signal lines.

- Create a homogeneous reference potential and ground all electrical operating supplies when possible.

- Please take care for the targeted employment of the grounding actions. The grounding of the PLC is a protection and functionality activity.

- Connect installation parts and cabinets with the System 200V in star topology with the isolation/protected earth conductor system. So you avoid ground loops.

- If potential differences between installation parts and cabinets occur, lay sufficiently dimensioned potential compensation lines.

Isolation of<br/>conductorsElectrical, magnetically and electromagnetic interference fields are<br/>weakened by means of an isolation, one talks of absorption.

Via the isolation rail, that is connected conductive with the rack, interference currents are shunt via cable isolation to the ground. Hereby you have to make sure, that the connection to the protected earth conductor is impedance-low, because otherwise the interference currents may appear as interference cause.

When isolating cables you have to regard the following:

- If possible, use only cables with isolation tangle.

- The hiding power of the isolation should be higher than 80%.

- Normally you should always lay the isolation of cables on both sides. Only by means of the both-sided connection of the isolation you achieve high quality interference suppression in the higher frequency area.

Only as exception you may also lay the isolation one-sided. Then you only achieve the absorption of the lower frequencies. A one-sided isolation connection may be convenient, if:

- the conduction of a potential compensating line is not possible

- analog signals (some mV res. µA) are transferred

- foil isolations (static isolations) are used.

- With data lines always use metallic or metalized plugs for serial couplings. Fix the isolation of the data line at the plug rack. Do not lay the isolation on the PIN 1 of the plug bar!

- At stationary operation it is convenient to strip the insulated cable interruption free and lay it on the isolation/protected earth conductor line.

- To fix the isolation tangles use cable clamps out of metal. The clamps must clasp the isolation extensively and have well contact.

- Lay the isolation on an isolation rail directly after the entry of the cable in the cabinet. Lead the isolation further on to the System 200V module and **don't** lay it on there again!

#### Please regard at installation!

At potential differences between the grounding points, there may be a compensation current via the isolation connected at both sides. Remedy: Potential compensation line.

# **General data**

| Structure/<br>dimensions | <ul> <li>Profile rail 35mm</li> <li>Peripheral modules with recessed labelling</li> <li>Dimensions of the basic enclosure:<br/>1tier width: (HxWxD) in mm: 76x25.4x74 in inches: 3x1x3<br/>2tier width: (HxWxD) in mm: 76x50.8x74 in inches: 3x2x3</li> </ul>                                                                                                                                                                                                                                         |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reliability              | <ul> <li>Wiring by means of spring pressure connections (CageClamps) at the front-facing connector, core cross-section 0.08 2.5mm<sup>2</sup> or 1.5mm<sup>2</sup> (18pole plug)</li> <li>Complete isolation of the wiring when modules are exchanged</li> <li>Every module is isolated from the backplane bus</li> <li>ESD/Burst acc. IEC 61000-4-2 / IEC 61000-4-4 (to level 3)</li> <li>Shock resistance acc. IEC 60068-2-6 / IEC 60068-2-27 (1G/12G)</li> <li>Class of protection IP20</li> </ul> |

| Environmental conditions | <ul> <li>Operating temperature: 0 +60°C</li> <li>Storage temperature: -25 +70°C</li> <li>Relative humidity: 5 95% without condensation</li> <li>Ventilation by means of a fan is not required</li> </ul>                                                                                                                                                                                                                                                                                              |

# Chapter 2 Hardware description

**Overview** Here the hardware components of the FM 250-1BA00 are described. The technical data are at the end of the chapter.

| Contents | Торіс        | Page                 |     |

|----------|--------------|----------------------|-----|

|          | Chapter 2    | Hardware description | 2-1 |

|          | Properties.  |                      |     |

|          | Structure    |                      | 2-3 |

|          | Technical of | data                 | 2-4 |

# **Properties**

**FM 250** 250-1BA00

- 2 channels with each 32Bit /

- 4 channels with each 16Bit (depending on the mode)

- DC 24V supply voltage via front and via backplane bus

- free configurable DC 24V outputs (max.1A)

- Counter and compare registers are loaded by means of a control byte

- Standard up-down counter with a resolution of 32Bit or 16Bit

- Compare and auto-reload functions

- Different modes for encoder pulses

- Pulse-width measurements and frequency measurements

#### Note!

The following information is only applicable to counter modules with order no.: VIPA 250-1BA00 and a revision level 5 and higher.

| Order data | Туре   | Order number   | Description                     |  |  |  |

|------------|--------|----------------|---------------------------------|--|--|--|

|            | FM 250 | VIPA 250-1BA00 | Counter module (2 counter 2 DO) |  |  |  |

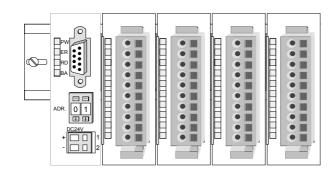

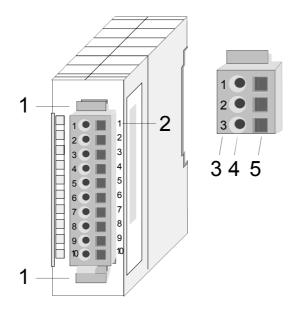

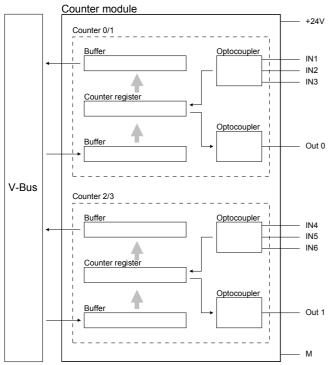

## Structure

**Functionality** The counter module accepts the signals from transducers connected to the module and processes these pulses in accordance with the selected mode of operation. The module has 2/4 channels with a data resolution of 32/16Bit each.

These modules provide 40 counter modes and two 24V outputs they are controlled in accordance with the selected mode.

# Status indicator pin assignment

Description

LED

|    | Description                                |                                                                                                                                                                                              |

|----|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L+ | LED (green)<br>Supply voltage<br>available | FM 250<br>2 Counter 2 DO                                                                                                                                                                     |

| 00 | LED (green)<br>Output counter 0            | $\rightarrow \bigcirc \bigcirc$     |

| O1 | LED (green)<br>Output counter 1            |                                                                                                                                                                                              |

| F  | LED (red)<br>Error /overload               | $\begin{array}{c} \bullet \\ \times \\ \times \\ 3 \\ 14 \\ \hline \end{array} \\ \hline \\ \bullet \\ \bullet$ |

#### Pin Assignment

| 1   | Supply voltage +24V DC  |

|-----|-------------------------|

| 2   | IN1 input 1 counter 0/1 |

| 3   | IN2 input 2 counter 0/1 |

| 4   | IN3 input 3 counter 0/1 |

| 5   | OUT0 output counter 0/1 |

| 6   | IN4 input 4 counter 2/3 |

| 7   | IN5 input 5 counter 2/3 |

| 8   | IN6 input 6 counter 2/3 |

| 9   | OUT1 output counter 2/3 |

| 4.0 |                         |

10 Common of supply voltage

#### Block diagram

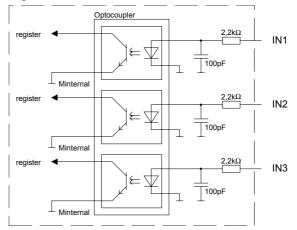

#### Input internal circuit

# **Technical data**

| Order number                                              | 250-1BA00    |

|-----------------------------------------------------------|--------------|

| Туре                                                      | FM 250       |

| Current consumption/power loss                            |              |

| Current consumption from backplane bus                    | 80 mA        |

| Power loss                                                | 2.5 W        |

| Technical data digital inputs                             |              |

| Number of inputs                                          | 6            |

| Cable length, shielded                                    | 1000 m       |

| Cable length, unshielded                                  | 600 m        |

| Rated load voltage                                        | DC 24 V      |

| Reverse polarity protection of rated load voltage         | $\checkmark$ |

| Current consumption from load voltage L+ (without load)   | -            |

| Rated value                                               | -            |

| Input voltage for signal "0"                              | DC 05 V      |

| Input voltage for signal "1"                              | DC 1528.8 V  |

| Input voltage hysteresis                                  | -            |

| Frequency range                                           | -            |

| Input resistance                                          | 2 kΩ         |

| Input current for signal "1"                              | 14 mA        |

| Connection of Two-Wire-BEROs possible                     | -            |

| Max. permissible BERO quiescent current                   | -            |

| Input delay of "0" to "1"                                 | 0,8 µs       |

| Input delay of "1" to "0"                                 | 0,8 µs       |

| Number of simultaneously utilizable inputs horizontal     | 6            |

| configuration                                             |              |

| Number of simultaneously utilizable inputs vertical       | 6            |

| configuration                                             |              |

| Input characteristic curve                                | -            |

| Initial data size                                         | 10 Byte      |

| Technical data digital outputs                            |              |

| Number of outputs                                         | 2            |

| Cable length, shielded                                    | 1000 m       |

| Cable length, unshielded                                  | 600 m        |

| Rated load voltage                                        | DC 24 V      |

| Reverse polarity protection of rated load voltage         | $\checkmark$ |

| Current consumption from load voltage L+ (without load)   | 10 mA        |

| Total current per group, horizontal configuration, 40°C   | -            |

| Total current per group, horizontal configuration, 60°C   | -            |

| Total current per group, vertical configuration           | -            |

| Output voltage signal "1" at min. current                 | L+ (-0.8 V)  |

| Output voltage signal "1" at max. current                 | -            |

| Output current at signal "1", rated value                 | 2 A          |

| Output current, permitted range to 40°C                   | -            |

| Output current, permitted range to 60°C                   | -            |

| Output current at signal "0" max. (residual current)      | -            |

| Output delay of "0" to "1"                                | max. 100 µs  |

| Output delay of "1" to "0"                                | max. 500 µs  |

| Minimum load current                                      | -            |

| Lamp load                                                 | 10 W         |

| Parallel switching of outputs for redundant control of a  | -            |

|                                                           |              |

| load                                                      |              |

| load<br>Parallel switching of outputs for increased power | -            |

|                                                           | -<br>-       |

| Order number                                                | 250-1BA00                               |

|-------------------------------------------------------------|-----------------------------------------|

| Switching frequency with inductive load                     | max. 0.5 Hz                             |

| Switching frequency on lamp load                            | max. 10 Hz                              |

| Internal limitation of inductive shut-off voltage           | L+ (-52 V)                              |

| Short-circuit protection of output                          | yes, electronic                         |

| Trigger level                                               | 3 A                                     |

| Number of operating cycle of relay outputs                  | -                                       |

| Switching capacity of contacts                              | -                                       |

| Output data size                                            | 10 Byte                                 |

| Technical data counters                                     |                                         |

| Number of counters                                          | 2                                       |

| Counter width                                               | 1x32 Bit / 2x16 Bit                     |

| Maximum input frequency                                     | 1 MHz                                   |

| Maximum count frequency                                     | 1 MHz                                   |

| Mode incremental encoder                                    | ✓ · · · · · · · · · · · · · · · · · · · |

| Mode pulse / direction                                      | ✓                                       |

| Mode pulse                                                  | $\checkmark$                            |

| Mode frequency counter                                      | ✓                                       |

| Mode period measurement                                     | ·<br>✓                                  |

| Gate input available                                        | ✓<br>✓                                  |

| Latch input available                                       |                                         |

| Reset input available                                       | -<br>-                                  |

| Counter output available                                    | ·<br>✓                                  |

| Status information, alarms, diagnostics                     |                                         |

| Status display                                              | Ves                                     |

| Interrupts                                                  | yes<br>no                               |

| Process alarm                                               | -                                       |

|                                                             | no                                      |

| Diagnostic interrupt<br>Diagnostic functions                | no                                      |

| •                                                           | no                                      |

| Diagnostics information read-out                            | none                                    |

| Supply voltage display                                      | yes                                     |

| Group error display                                         | red LED                                 |

| Channel error display                                       | none                                    |

| Isolation                                                   |                                         |

| Between channels                                            | -                                       |

| Between channels of groups to                               | -                                       |

| Between channels and backplane bus                          | ✓                                       |

| Between channels and power supply                           | -                                       |

| Max. potential difference between circuits                  | -                                       |

| Max. potential difference between inputs (Ucm)              | -                                       |

| Max. potential difference between Mana and Mintern (Uiso)   | -                                       |

| Max. potential difference between inputs and Mana (Ucm)     | -                                       |

| Max. potential difference between inputs and Mintern (Uiso) | -                                       |

| Max. potential difference between Mintern and outputs       | -                                       |

| Insulation tested with                                      | DC 500 V                                |

| Datasizes                                                   |                                         |

| Input bytes                                                 | 10                                      |

| Output bytes                                                | 10                                      |

| Parameter bytes                                             | 4                                       |

| Diagnostic bytes                                            | 0                                       |

| Housing                                                     |                                         |

| Material                                                    | PPE / PA 6.6                            |

| Mounting                                                    | Profile rail 35 mm                      |

| Mechanical data                                             |                                         |

|                                                             | 25 4 x 76 x 70 mm                       |

| Dimensions (WxHxD)                                          | 25.4 x 76 x 78 mm                       |

| Order number             | 250-1BA00       |

|--------------------------|-----------------|

| Weight                   | 230 g           |

| Environmental conditions |                 |

| Operating temperature    | 0 °C to 60 °C   |

| Storage temperature      | -25 °C to 70 °C |

| Certifications           |                 |

| UL508 certification      | yes             |

# Chapter 3 Deployment

**Overview** This chapter provides information to the configuration and the various counter modes of the Counter module FM 250 are described.

# ContentsTopicPageChapter 3Deployment3-1Data input / output3-2Summary of counter modes and interfacing3-3Counter modes3-6

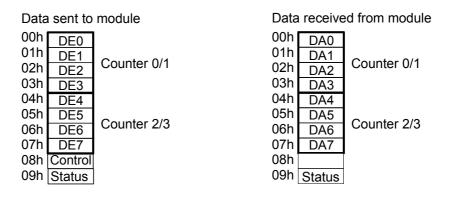

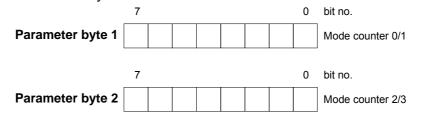

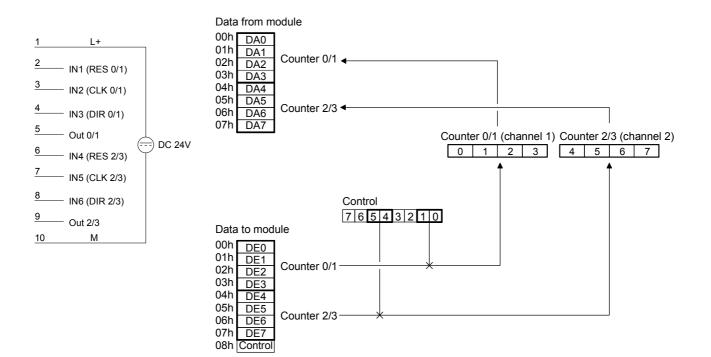

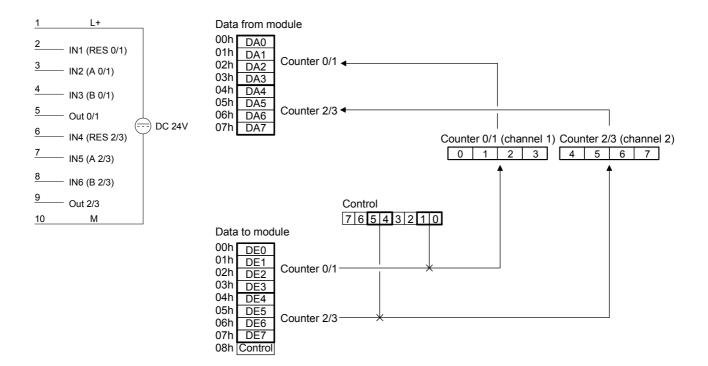

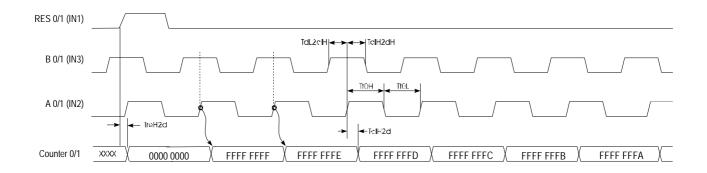

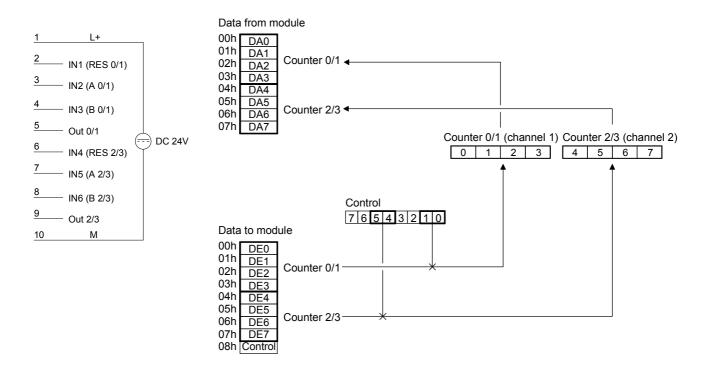

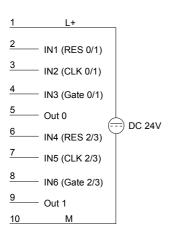

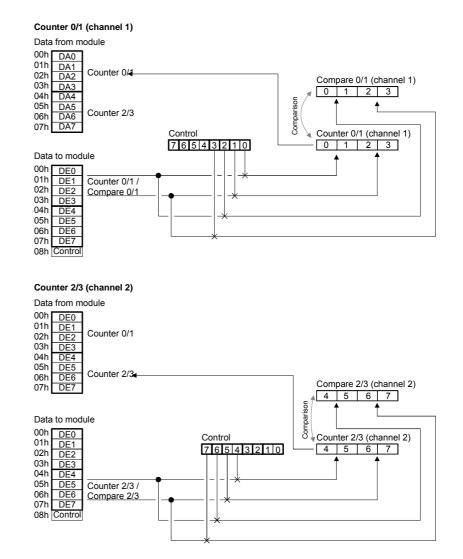

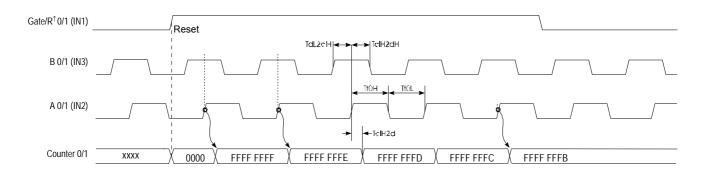

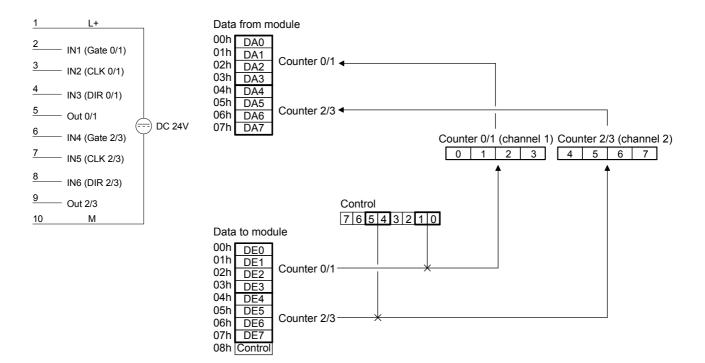

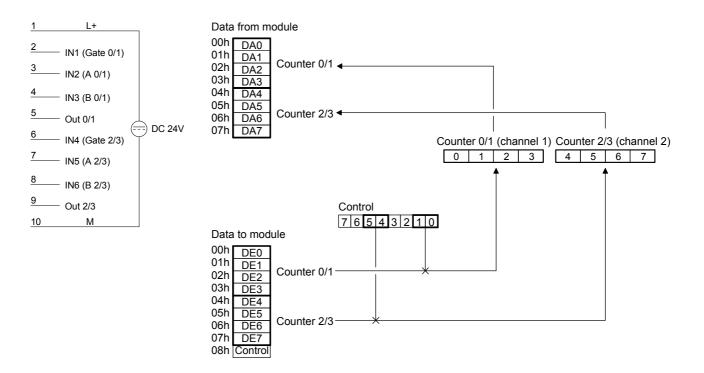

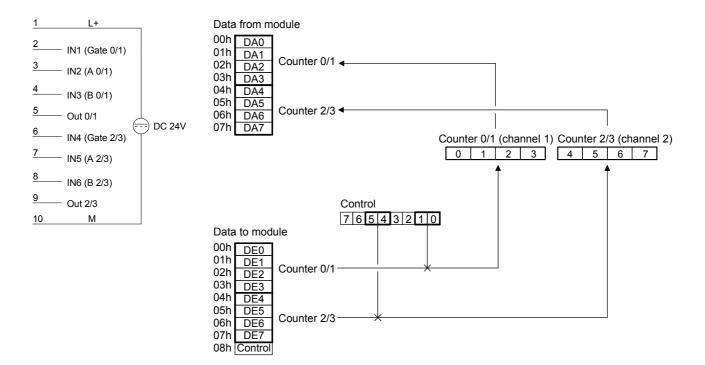

## Data input / output

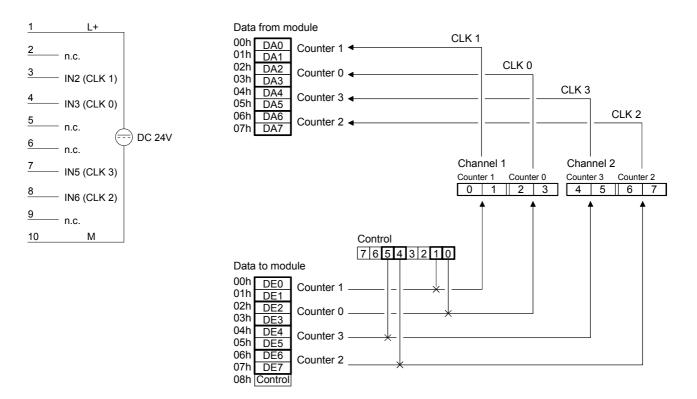

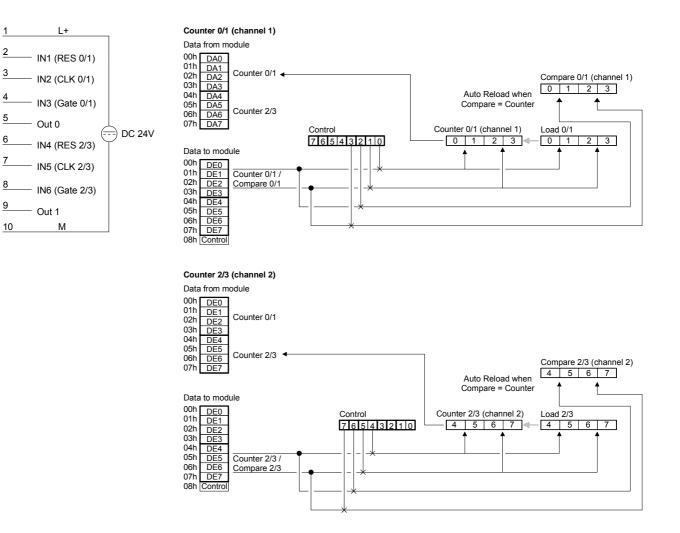

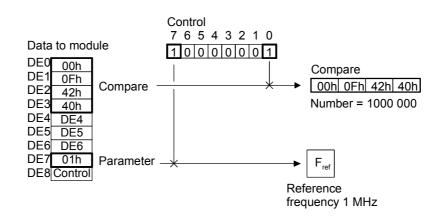

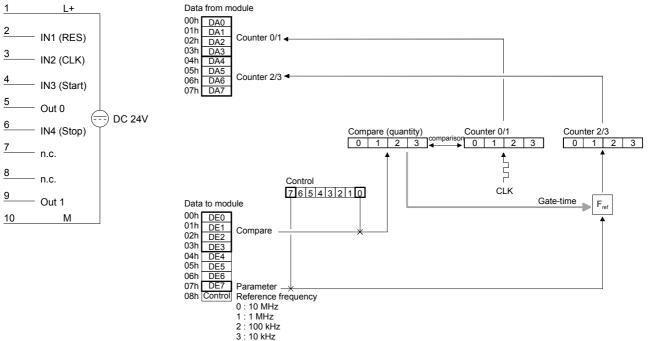

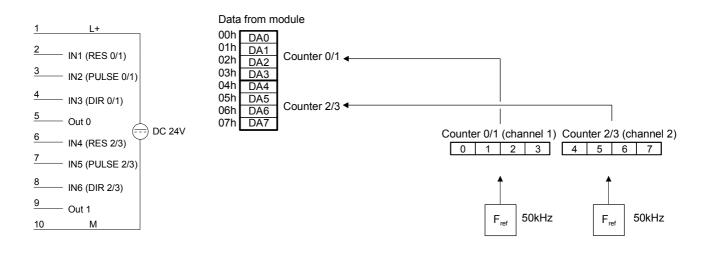

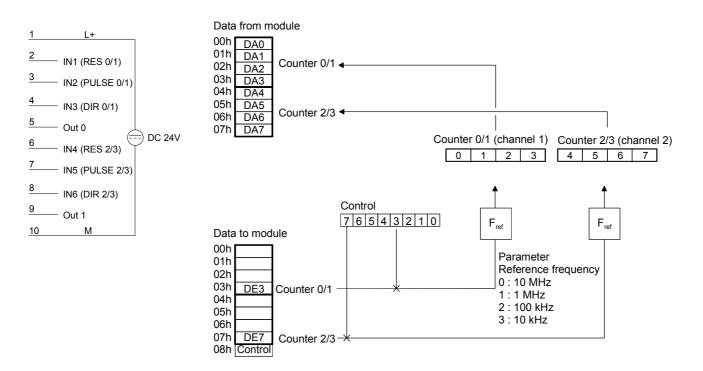

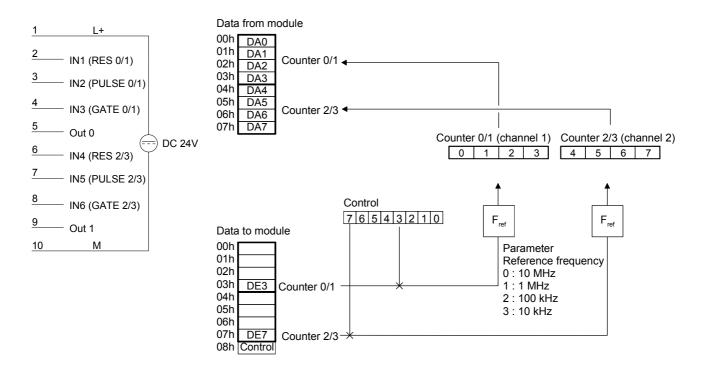

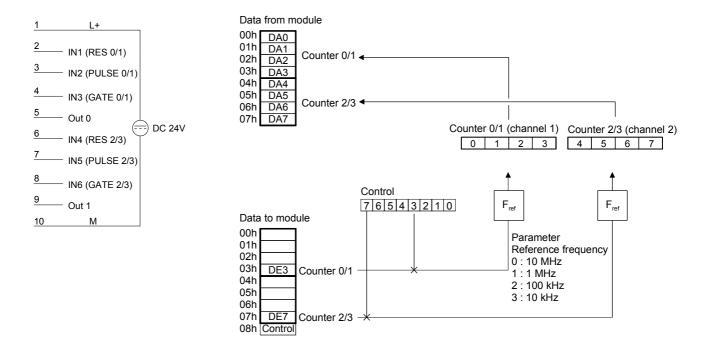

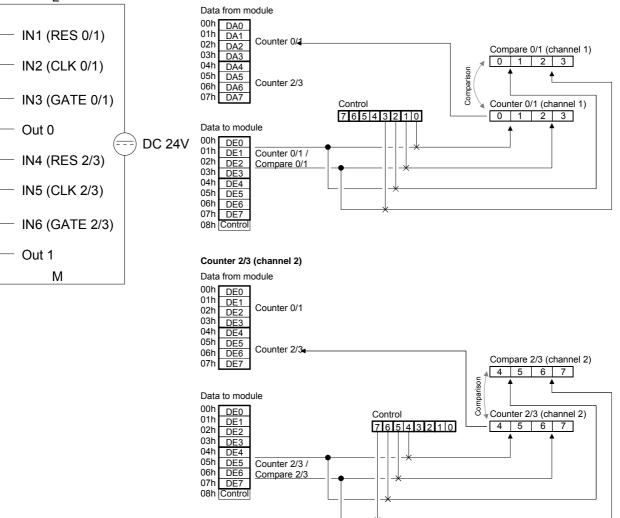

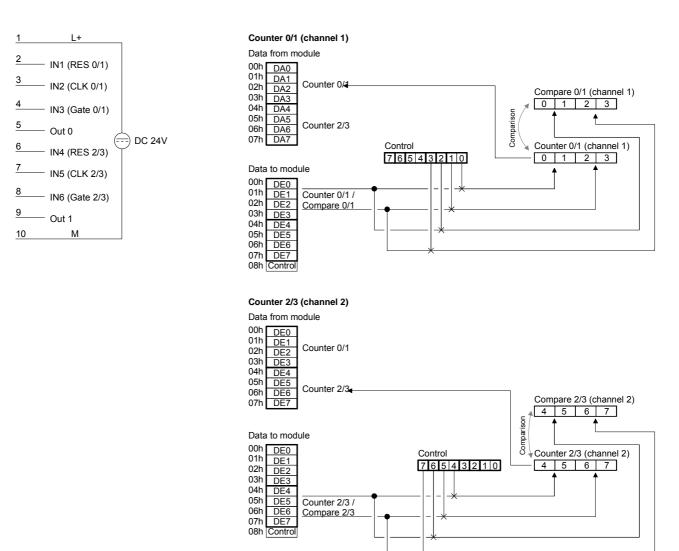

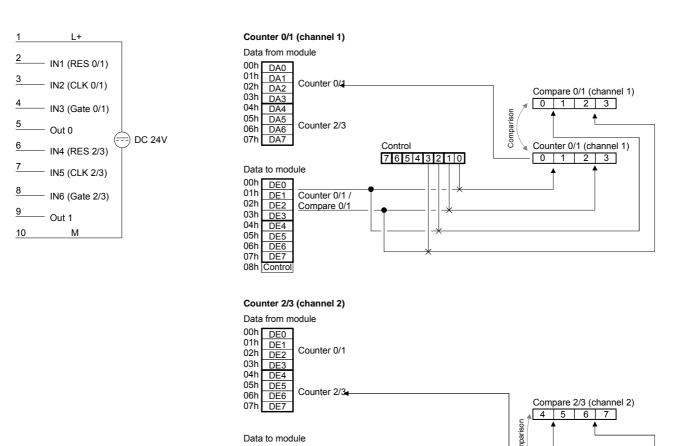

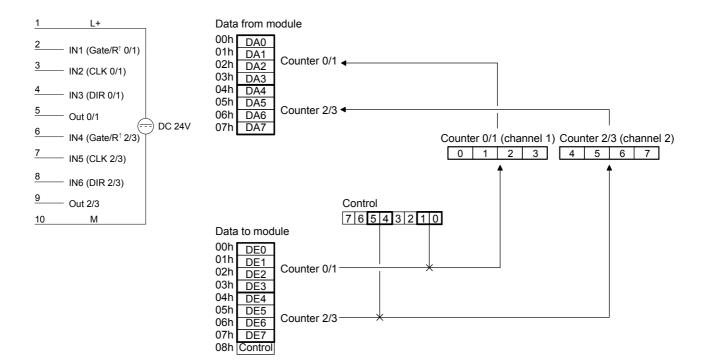

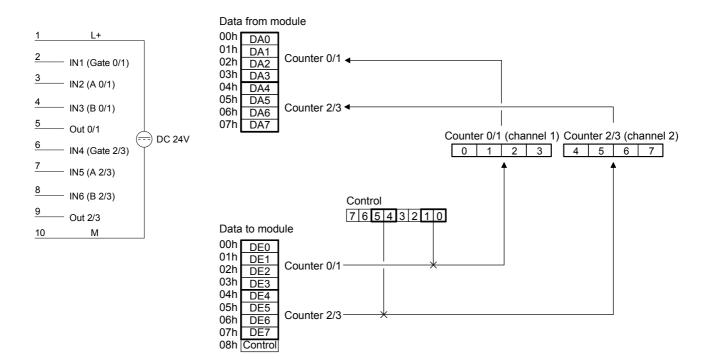

Access to the The module has 2/4 channels with a resolution of 32/16Bit each. You may use parameters to specify the mode for each channel res. channel pair. The pin assignment for the channel depends upon the selected mode (see description of modes).

10 data bytes are required for the data input and output. Data output to a counter channel requires 10Byte, for example for defaults or for comparison values. In the latter case Byte 9 (control) is used to initiate a write operation into the required counter register. The respective values are transferred into the counter registers when they are toggled  $(0 \rightarrow 1)$ .

The 10. byte (status byte) controls the behavior of the counter during a restart of the next higher master module. You may set the counter level to retentive by means of a combination of Bits 0 and 1; i.e. the original counter level will not be reset when the next higher master module restarts.

The following combinations are possible:

| Bit 0 = 1, Bit 1 = 0 | counter value is retentive during restart       |

|----------------------|-------------------------------------------------|

| Bit 0 = x, Bit 1 = 1 | counter value is reset during restart (default) |

You may check your settings at any time by reading Byte 10 of the output data.

**Configuration parameters** The configuration parameters consist of 2Byte. You use these bytes to define the operating mode of each channel by means of a mode number. This chapter contains a detailed description of the different modes further below. The different combinations of the various modes are available from the table on the next page. The procedure for the transfer of parameter bytes is available from the description for the System 200V bus coupler or the master system.

# Summary of counter modes and interfacing

| Mode | may<br>be<br>combi<br>ned | Function                                        | IN1                 | IN2      | IN3     | IN4    | IN5              | IN6     | OUT0            | OUT1            | Auto<br>Re-<br>Ioad | Com-<br>pare<br>Load |

|------|---------------------------|-------------------------------------------------|---------------------|----------|---------|--------|------------------|---------|-----------------|-----------------|---------------------|----------------------|

|      | nou                       |                                                 | Co                  | unter 0  | /1      | Cc     | ounter 2         | 2/3     |                 |                 |                     | 1                    |

| 0    | yes                       | 32bit counter                                   | RES                 | CLK      | DIR     | RST    | CLK              | DIR     | =0              | =0              | no                  | =0                   |

| 1    | yes                       | Encoder 1 edge                                  | RES                 | Α        | В       | RST    | Α                | В       | =0              | =0              | no                  | =0                   |

| 3    | yes                       | Encoder 2 edges                                 | RES                 | Α        | В       | RST    | Α                | В       | =0              | =0              | no                  | =0                   |

| 5    | yes                       | Encoder 4 edges                                 | RES                 | Α        | В       | RST    | Α                | В       | =0              | =0              | no                  | =0                   |

|      |                           |                                                 | Counte              | er 1 cou | intor 0 | Count  | er 3 cou         | inter 2 |                 |                 |                     |                      |

| 8    | 1/00                      | 2x16bit counter up/up                           | -                   | CLK      | CLK     |        | CLK              |         | -               | -               | 20                  |                      |

| 9    | yes<br>ves                | 2x16bit counter down/up                         | -                   | CLK      | CLK     | -      | CLK              | CLK     | -               | -               | no<br>no            | no<br>no             |

| 10   | yes                       | 2x16bit counter up/down                         | _                   | CLK      | CLK     | -      | CLK              | CLK     | -               | -               | no                  | no                   |

| 10   | yes                       | 2x16bit counter                                 | -                   | CLK      | CLK     | -      | CLK              | CLK     | -               | -               | no                  | no                   |

|      | ,00                       | down/down                                       |                     | OLIN     | OLIX    |        | OEIX             | OLIX    |                 |                 | 110                 | 110                  |

|      |                           |                                                 | <u> </u>            | unter 0  | //1     | 6      | ounter 2         | 0/2     |                 |                 |                     |                      |

| 12   | yes                       | 32bit counter up + gate                         | RES                 | CLK      | Gate    | RST    | CLK              | Gate    | =comp           | =comp           | no                  | yes                  |

| 12   | yes                       | 32bit counter down + gate                       |                     | CLK      | Gate    | RST    | CLK              | Gate    | =comp           | =comp           | no                  | yes                  |

| 13   | yes                       | 32bit counter up + gate                         | RES                 | CLK      | Gate    | RST    | CLK              | Gate    | =comp           | =comp           | yes                 | yes                  |

| 15   | ves                       | 32bit counter down + gate                       |                     | CLK      | Gate    | RST    | CLK              | Gate    | =comp           | =comp           | ves                 | yes                  |

| 10   | yco                       | ozbit obuliter down - gate                      | NL0                 | OER      | Outo    | Rot    | OLIX             | Oute    | oomp            | oomp            | yco                 | yco                  |

|      |                           | I                                               | -                   | 1        |         | counte | r 03             |         |                 | 1               | 1                   | 1                    |

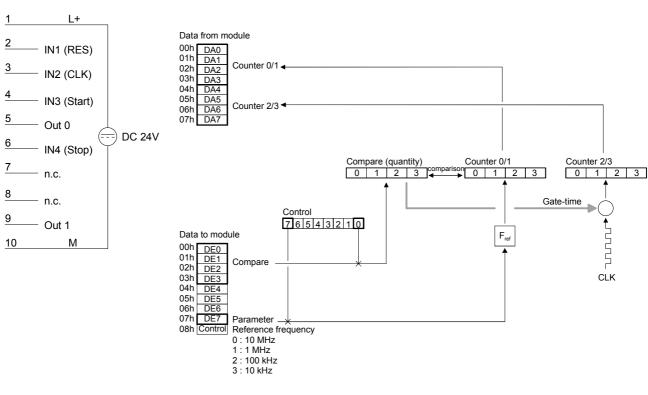

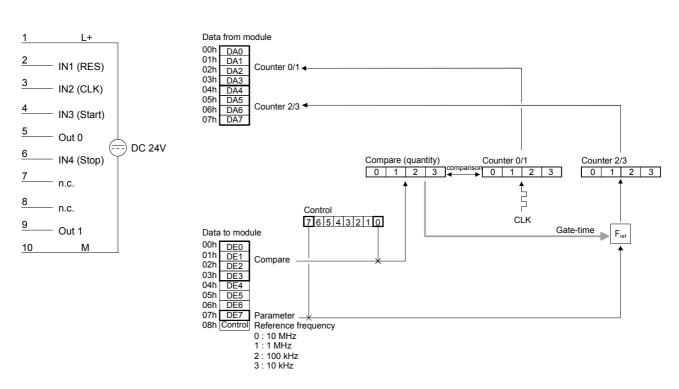

| 16   | no                        | Frequency measurement                           | RES                 | CLK      | Start   | Stop   | -                | -       | Meas.<br>active | Meas.<br>compl. | no                  | yes                  |

| 17   | no                        | Period measurement                              | RES                 | CLK      | Start   | Stop   | -                | -       | Meas.<br>active | Meas.<br>compl. | no                  | yes                  |

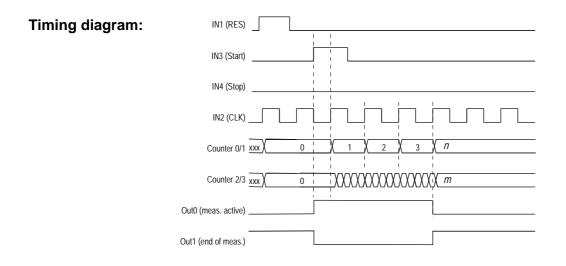

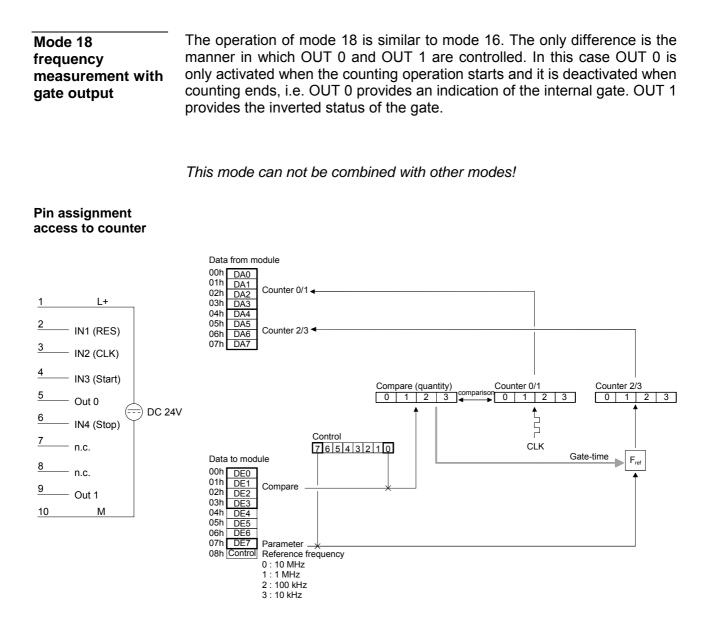

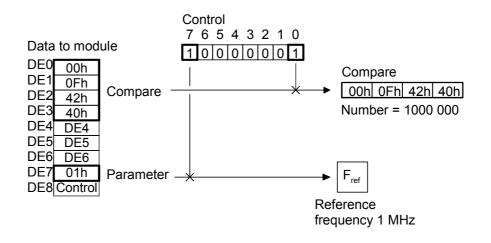

| 18   | no                        | Frequency measurement with gate output          | RES                 | CLK      | Start   | Stop   | -                | -       | Meas.<br>gate   | Meas.<br>gate   | no                  | yes                  |

| 19   | no                        | Period measurement with gate output             | RES                 | CLK      | Start   | Stop   | -                | -       | Meas.<br>gate   | Meas.<br>gate   | no                  | yes                  |

|      |                           |                                                 |                     |          |         |        |                  |         |                 |                 | •                   |                      |

|      |                           | D. I. 50111                                     |                     | unter 0  |         |        | ounter 2         |         |                 | r               |                     | 1                    |

| 6    | yes                       | Pulse low, 50kHz with<br>Direction Input        | RES                 | Pulse    | DIR     | RES    | Pulse            | DIR     | -               | -               |                     |                      |

| 20   | yes                       | Pulse low, prog. time base with Direction Input | RES                 | Pulse    | DIR     | RES    | Pulse            | DIR     | -               | -               |                     |                      |

| 21   | yes                       | Pulse low, up, prog. time<br>base with Gate     | RES                 | Pulse    | Gate    | RES    | Pulse            | Gate    | -               | -               |                     |                      |

| 22   | yes                       | Pulse high, up, prog. time base with Gate       | RES                 | Pulse    | Gate    | RES    | Pulse            | Gate    | -               | -               |                     |                      |

|      |                           |                                                 | Co                  | unter 0  | /1      | Co     | ounter 2         | 2/3     |                 |                 |                     |                      |

| 23   | yes                       | One Shot, up, Set                               | RES                 | CLK      | Gate    | RES    | CLK              | Gate    | 1 if<br>active  | 1 if<br>active  | no                  | yes                  |

| 24   | yes                       | One Shot, down, Set                             | RES                 | CLK      | Gate    | RES    | CLK              | Gate    | 1 if<br>active  | 1 if<br>active  | no                  | yes                  |

| 25   | yes                       | One Shot, up, Reset                             | RES                 | CLK      | Gate    | RES    | CLK              | Gate    | 0 if<br>active  | 0 if<br>active  | no                  | yes                  |

| 26   | yes                       | One Shot, down, Reset                           | RES                 | CLK      | Gate    | RES    | CLK              | Gate    | 0 if<br>active  | 0 if<br>active  | no                  | yes                  |

|      |                           |                                                 | C ~                 | unter 0/ | /1      |        | ounter           | 2/3     |                 |                 |                     |                      |

| 27   | VOS                       | 32 bit counter                                  | Gate/R <sup>↑</sup> | CLK      | DIR     |        |                  |         | =0              | =0              | <b>P</b> O          | =0                   |

| 27   | yes                       | Encoder 1 edge                                  |                     |          | B       | Gate/R |                  | B       | =0<br>=0        | =0              | no                  | =0                   |

| 20   | yes                       | Encoder 2 edges                                 | Gate/R <sup>↑</sup> | A        | B       | Gate/R |                  | B       | =0              | =0              | no                  | =0                   |

|      | yes                       | -                                               | Gate/R <sup>↑</sup> | A        |         | Gate/R |                  |         | -               | _               | no                  | =0                   |

| 30   | yes                       | Encoder 4 edges                                 | Gate/R <sup>T</sup> | A        | В       | Gate/R | R <sup>T</sup> A | В       | =0              | =0              | no                  |                      |

continued ...

... continue

| Mode | may<br>be<br>com-<br>bined | Function                | IN1              | IN2      | IN3  | IN4              | IN5      | IN6  | OUT0  | OUT1  | Auto<br>Re-<br>Ioad | Com-<br>pare<br>Load |

|------|----------------------------|-------------------------|------------------|----------|------|------------------|----------|------|-------|-------|---------------------|----------------------|

|      |                            |                         | 6                | ounter 0 | /1   | C                | ounter 2 | 0/3  | 1     |       |                     |                      |

| 31   | yes                        | 32Bit counter up+Gate   | RES <sup>↑</sup> |          | Gate | RES <sup>↑</sup> | CLK      | Gate | =comp | =comp | no                  | yes                  |

| 32   | ves                        | 32Bit counter down+Gate | RES <sup>↑</sup> | CLK      | Gate | RES <sup>↑</sup> | CLK      | Gate | =comp | =comp | no                  | ves                  |

| 33   | yes                        | 32Bit counter up+Gate   | RES <sup>↑</sup> | CLK      | Gate | RES <sup>↑</sup> | CLK      | Gate | =comp | =comp | yes                 | yes                  |

| 34   | yes                        | 32Bit counter down+Gate | RES <sup>↑</sup> | CLK      | Gate | RES <sup>↑</sup> | CLK      | Gate | =comp | =comp | yes                 | yes                  |

|      | 1                          | 0001                    |                  | ounter 0 |      |                  | ounter 2 |      |       |       | 1                   | -                    |

|      |                            |                         | Co               | ounter 0 | /1   | Co               | ounter 2 | 2/3  |       |       |                     |                      |

| 35   | yes                        | 32Bit counter           | Gate             | CLK      | DIR  | Gate             | CLK      | DIR  | =0    | =0    | no                  | =0                   |

| 36   | yes                        | Encoder 1 edge          | Gate             | A        | В    | Gate             | А        | В    | =0    | =0    | no                  | =0                   |

| 37   | yes                        | Encoder 2 edges         | Gate             | A        | В    | Gate             | Α        | В    | =0    | =0    | no                  | =0                   |

| 38   | yes                        | Encoder 4 edges         | Gate             | Α        | В    | Gate             | А        | В    | =0    | =0    | no                  | =0                   |

|      |                            |                         |                  |          |      |                  |          |      |       |       |                     |                      |

|      |                            |                         | Co               | ounter 0 | /1   | Co               | ounter 2 | 2/3  |       |       |                     |                      |

| 39   | yes                        | 32Bit counter up+Gate   | RES <sup>↑</sup> | Gate     |      | RES <sup>↑</sup> | Gate     |      | -     | -     | -                   | -                    |

| 40   | yes                        | 32Bit counter down+Gate | RES <sup>⊺</sup> | Gate     |      | RES <sup>↑</sup> | Gate     |      | -     | -     | -                   | -                    |

| 41   | yes                        | 32Bit counter up+Gate   | RES <sup>↑</sup> | Gate     |      | RES <sup>↑</sup> | Gate     |      | -     | -     | -                   | -                    |

| 42   | yes                        | 32Bit counter down+Gate | RES <sup>↑</sup> | Gate     |      | RES <sup>↑</sup> | Gate     |      | -     | -     | -                   | -                    |

Due to technical advances the revision level and the functionality of the counter module was continuously expanded. Below follows a list that allocates the different modes to the revision level:

| Mode 0-5      | revision level 3   | Mode 27-30 | revision level 8/9 |

|---------------|--------------------|------------|--------------------|

| Mode 0-17     | revision level 4   | Mode 31-38 | revision level 10  |

| Mode 0-19     | revision level 5   | Mode 39-42 | revision level 11  |

| Mode 6, 20-26 | revision level 6/7 |            |                    |

#### Terminology:

| RES              | RESET signal that has to be LOW during the measuring process. A HIGH level (level triggered) erases one or both counters, depending on the selected mode.       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RES <sup>↑</sup> | The counter is reset by the rising edge of this signal (edge triggered).                                                                                        |

| CLK              | The clock signal from the connected transducer.                                                                                                                 |

| Start or Stop    | A HIGH level starts or stops the counter. When the start level is active, the counter will start with the next CLK pulse that corresponds to the selected mode. |

| DIR              | In mode 0 the level of the DIR signal determines the direction of the counting process.<br>LOW level: count up<br>HIGH level: count down                        |

| Auto Reload         |                                      | function transfers a user-defined value into the counter reaches the number contained in the compare register.                                |

|---------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Compare Load        |                                      | compare function to specify an stop value for the counter.<br>selected mode an output is activated or the counter is re-<br>aches this value. |

| Gate                | Gate signal enabli                   | ing the counter.                                                                                                                              |

| Gate/R <sup>↑</sup> | is at "1", the count                 | set by the rising edge of this signal. As long as the signal ter is released.<br>ered; $R^{\uparrow}$ = edge triggered)                       |

| Measurement gate    |                                      | f the counter activity - is set to a HIGH level after the 1.<br>OW level after the last CLK signal (mode 18 19).                              |

| Pulse               | The pulse width o internal time base | of the introduced signal is determined by means of the .                                                                                      |

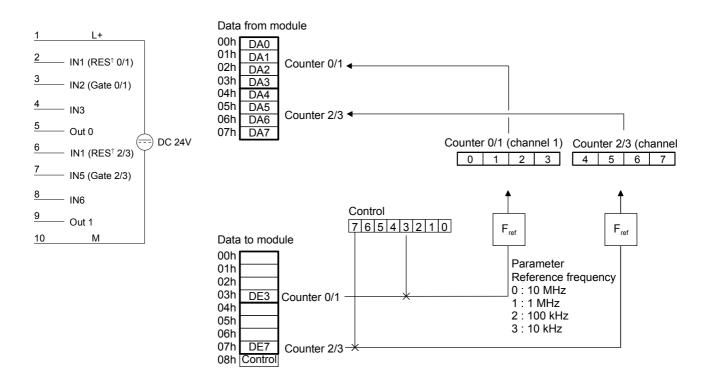

| Fref                |                                      | k frequency that is set permanently to 50kHz in mode 6.<br>cy "Fref" for counter modes 20-22, 39-42 is programmable:                          |

|                     | Parameter                            | Fref                                                                                                                                          |

|                     | 0                                    | 10MHz                                                                                                                                         |

|                     | 1                                    | 1MHz                                                                                                                                          |

|                     | 2                                    | 100kHz                                                                                                                                        |

|                     | 3                                    | 10kHz                                                                                                                                         |

# **Counter modes**

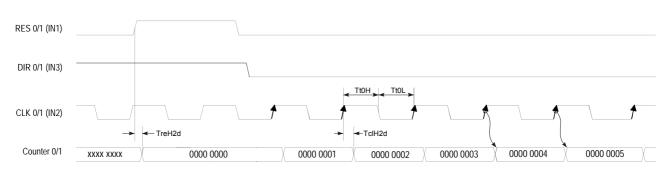

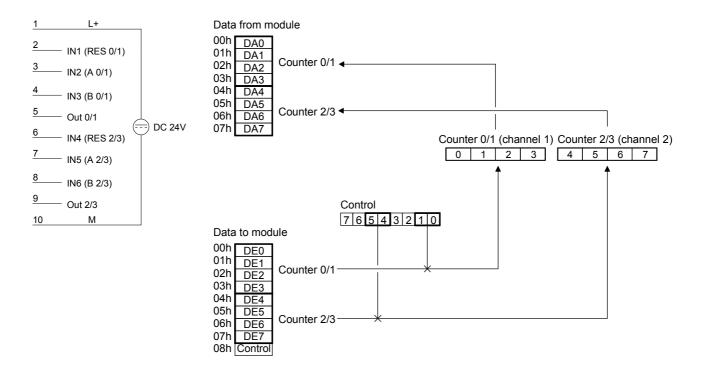

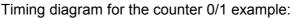

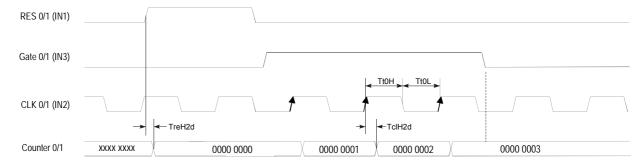

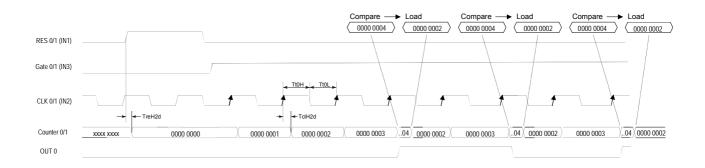

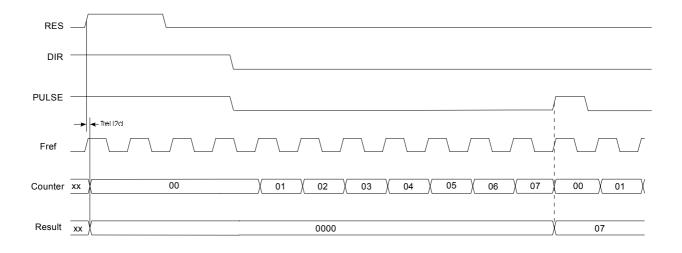

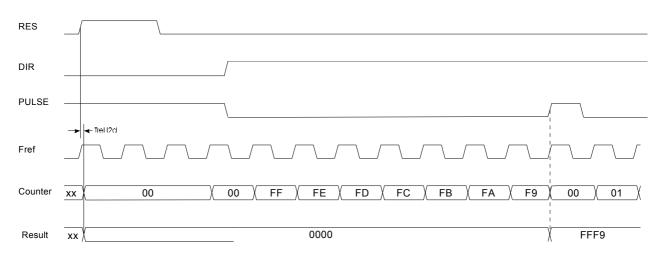

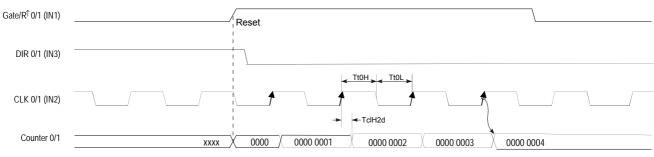

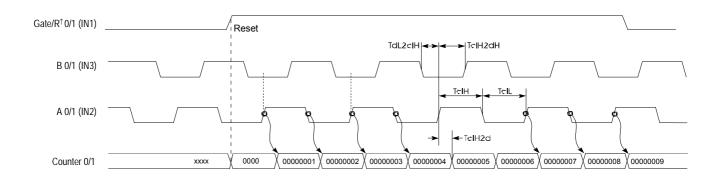

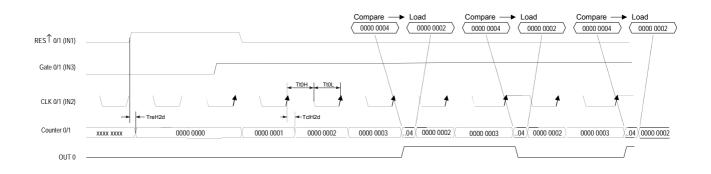

Mode 0<br/>32Bit counter2x 32Bit Counter. You determine the direction by means of the DIR input<br/>(IN3 or IN6). Every rising or falling edge of the input clock signal increments<br/>or decrements the counter. During the counting process the RES signal<br/>must be at a LOW level. If the RES signal is at a HIGH level, the counter is<br/>cleared. When the counter reaches zero, output OUT of the respective<br/>counter is active for a minimum period of 100ms, even if the counter should<br/>continue counting. If the counter stops at zero, the output remains active.

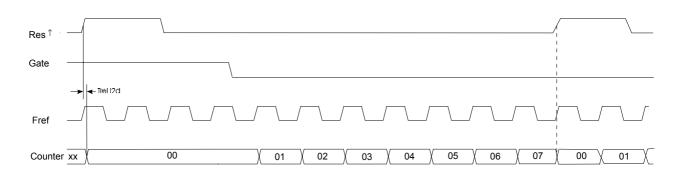

# Up counter

In mode 0, a LOW level at the DIR input configures the counter for counting up.

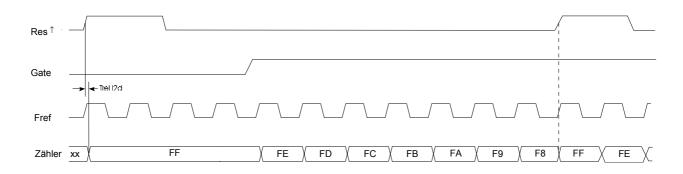

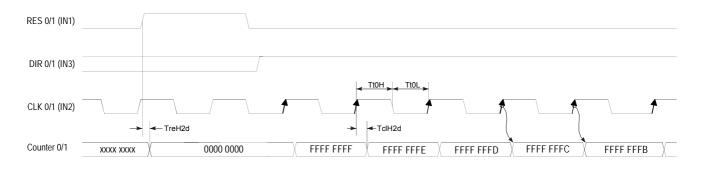

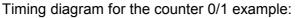

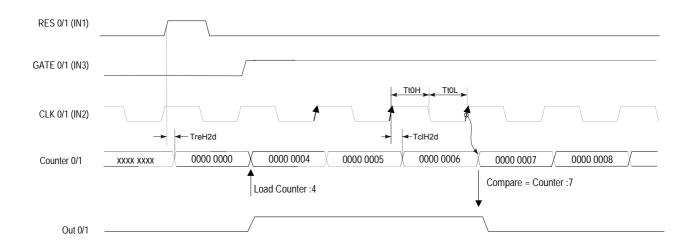

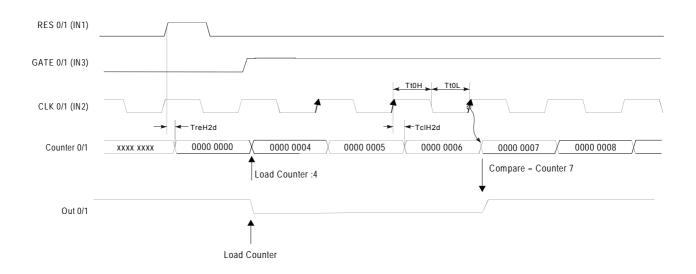

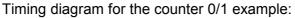

Timing diagram of the counter 0/1 example:

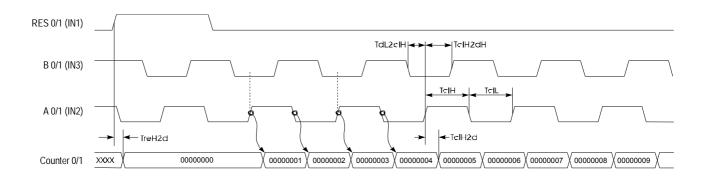

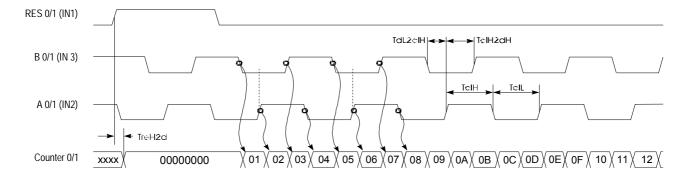

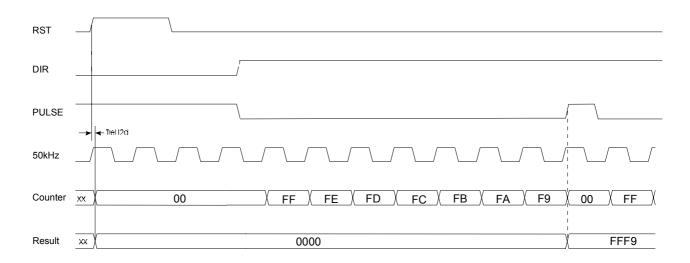

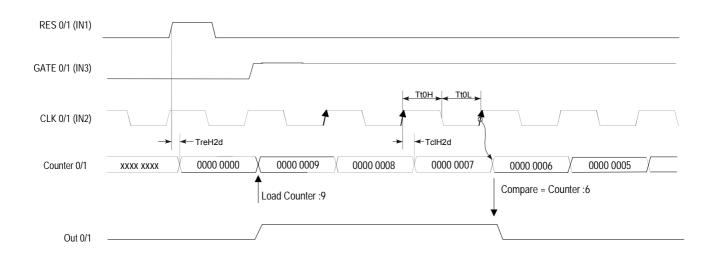

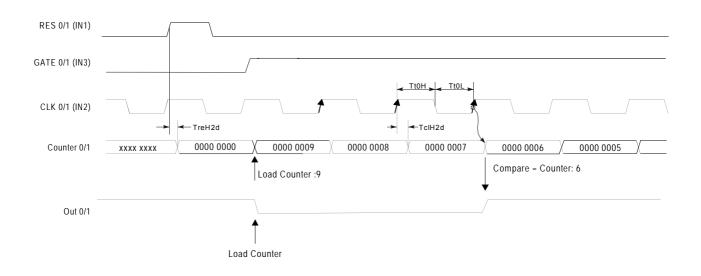

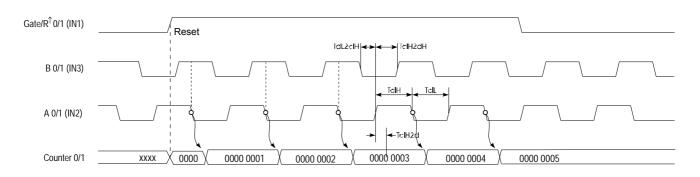

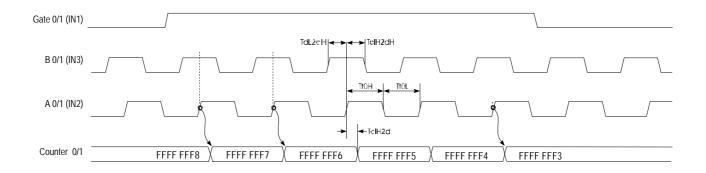

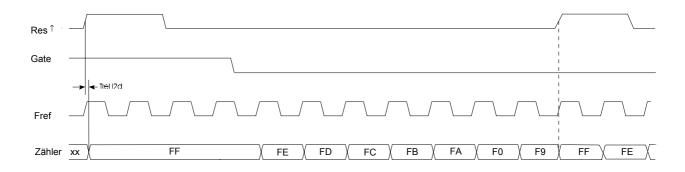

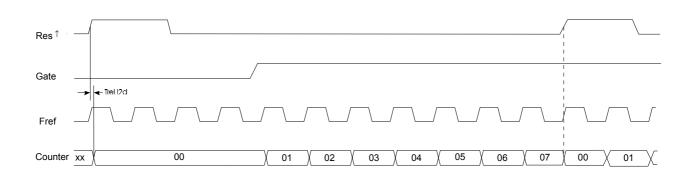

# **Down counter** In mode 0, a HIGH level at the DIR input configures the counter for counting down. Timing diagram of the counter 0/1 example:

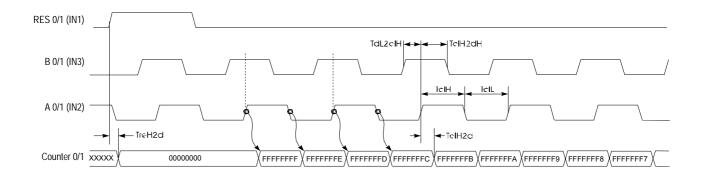

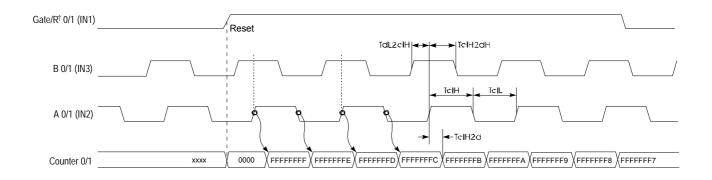

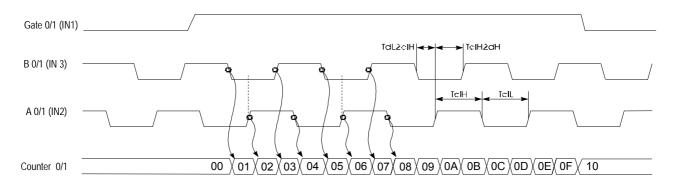

### Mode 1 Encoder 1 edge In mode 1 you may configure an encoder for one of the channels. Depending on the direction of rotation this encoder will increment or decrement the internal counter with every falling edge. The RES input has to be at a LOW level during the counting process. A HIGH level clears the counter. When the counter reaches zero, output OUT of the respective counter is active for a minimum period of 100ms, even if the counter continues counting. If the counter stops at zero the output remains active.

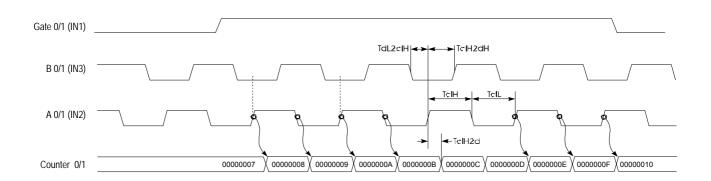

# Up counter Every falling edge of the signal at input A increments the counter if input B is at HIGH level at this moment.

# **Down counter** Every rising edge of the signal at input A decrements the internal counter if input B is at HIGH level at this moment. Timing diagram for the counter 0/1 example:

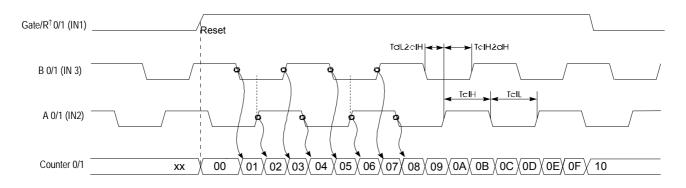

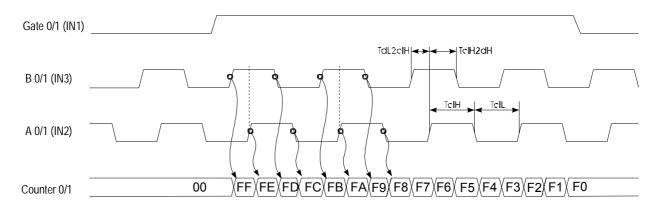

## Mode 3 Encoder 2 edges

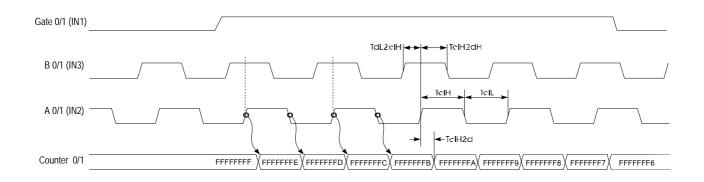

Every rising or falling edge of the signal at input A changes the counter by 1. The direction of the count depends on the level of the signal applied to input B. RES has to be at a LOW level during the counting process. A HIGH level clears the counter. When the counter reaches zero, output OUT of the respective counter is active for a minimum period of 100ms, even if the counter continues counting. If the counter stops at zero the output remains active.

# **Up counter** The counter is incremented by the rising edge of signal A if input B is at a LOW level or by the falling edge of input A when input B is at a HIGH level. Timing diagram for the counter 0/1 example:

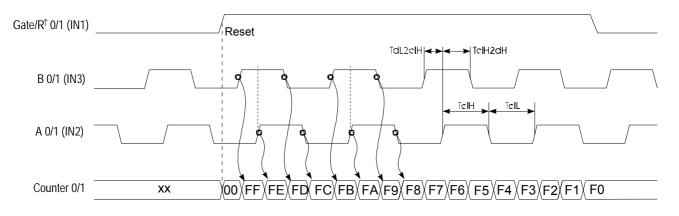

# **Down-counter** The counter is decremented by the rising edge of signal A if input B is at a HIGH level or by the falling edge of input A when input B is at a LOW level. Timing diagram for the counter 0/1 example:

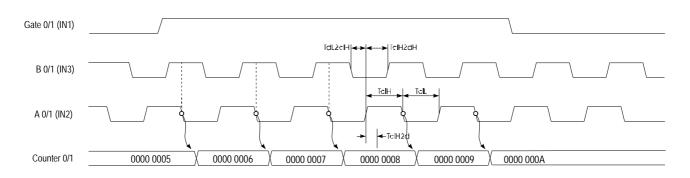

## Mode 5 Encoder 4 edges

Every rising or falling edge at inputs A or B increments or decrements the counter. The direction depends on the level applied to the other input (B or A). RES has to be at a LOW level during the counting process. A HIGH level clears the counter. When the counter reaches zero, output OUT of the respective counter is active for a minimum period of 100ms, even if the counter continues counting. If the counter stops at zero, the output remains active.

**Up counter** The counter is incremented when a rising edge is applied to B while input A is at a HIGH level or if a falling edge is applied to B when input A is at a LOW level. Alternatively it is also incremented when a rising edge is applied to A when input B is at a LOW level or by a falling edge at A when input B is at a HIGH level.

**Down counter** The counter is decremented when a rising edge is applied to B while input A is at a LOW level or if a falling edge is applied to B when input A is at a HIGH level. Alternatively it is also decremented when a rising edge is applied to A when input B is at a HIGH level or by a falling edge at input A when input B is at a LOW level.

Timing diagram for counter 0/1 example:

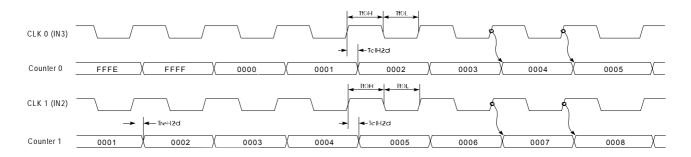

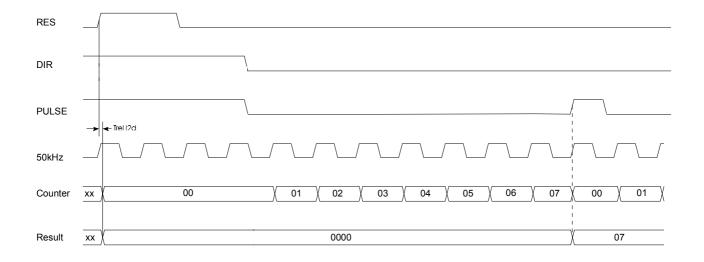

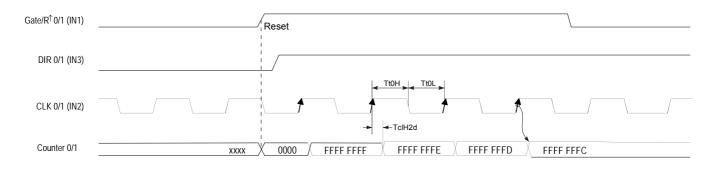

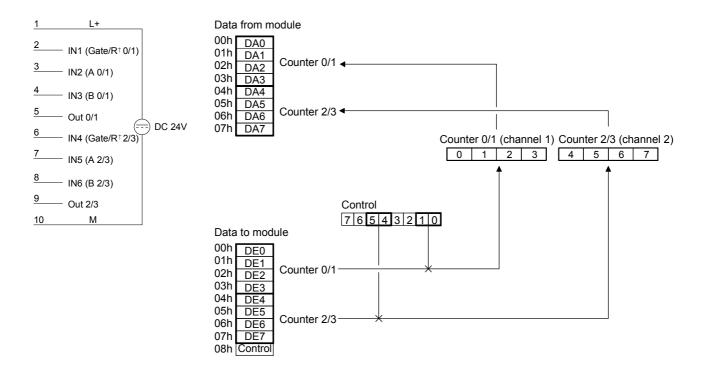

| Mode 8 11<br>two input counter<br>function | In this mode each channel provides 2 counters of 16Bit each. The rising edge of the input clock CLK x increments or decrements the respective counter. In this mode each counter can also be preset to a certain value by means of a control bit. Outputs are not available. A RESET is also not available. The following combinations are possible for every channel: |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | Mode 8 - counter 0/1 up, counter 2/3 up                                                                                                                                                                                                                                                                                                                                |

Mode 8 - counter 0/1 up, counter 2/3 up Mode 9 - counter 0/1 down, counter 2/3 up Mode 10 - counter 0/1 up, counter 2/3 down Mode 11 - counter 0/1 down, counter 2/3 down

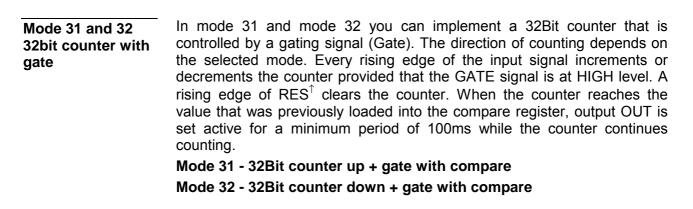

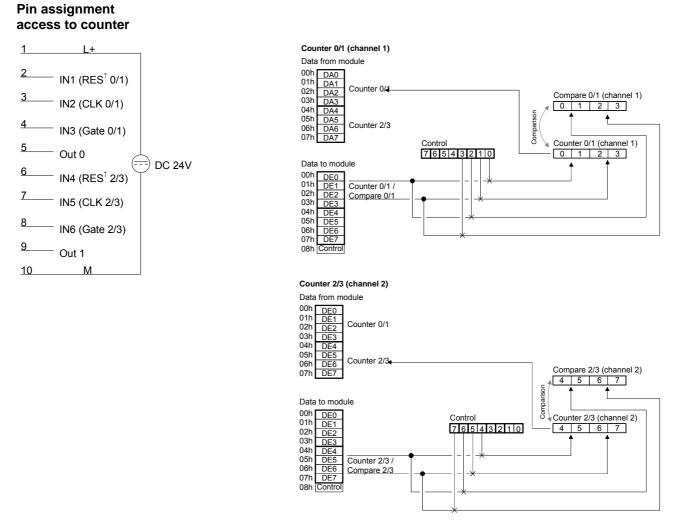

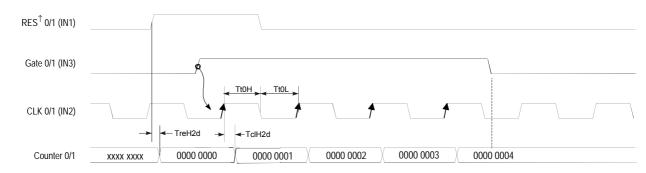

# Pin assignment access to counter

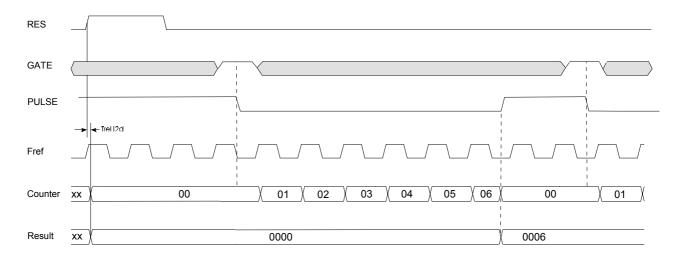

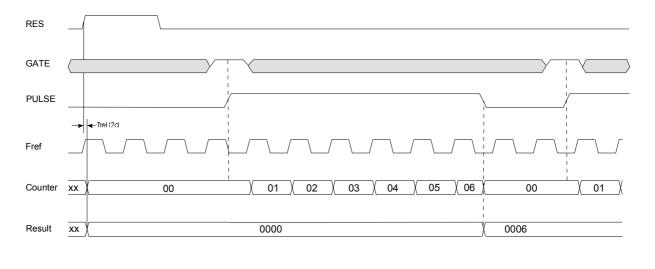

## **Timing diagram**

Below follows a timing diagram depicting an example of counter 0 and counter 1 in mode 8:

| Mode 12 and 13<br>32bit counter with<br>gate                                                                                    | In mode 12 and mode 13 you can implement a 32Bit counter that is<br>controlled by a gating signal (Gate). The direction of counting depends on<br>the selected mode. Every rising edge of the input signal increments or<br>decrements the counter provided that the GATE signal is at HIGH level.<br>RES has to be LOW during the counting process. A HIGH level clears the<br>counter. When the counter reaches the value that was previously loaded<br>into the compare register, output OUT is set active for a minimum period of<br>100ms while the counter up + gate with compare<br>Mode 12 - 32Bit counter up + gate with compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|