##

# **VIPA System 300S**

SPEED7 - CPU | 315-2AG12 | Manual HB140E\_CPU | RE\_315-2AG12 | Rev. 12/06

February 2012

#### Copyright © VIPA GmbH. All Rights Reserved.

This document contains proprietary information of VIPA and is not to be disclosed or used except in accordance with applicable agreements.

This material is protected by the copyright laws. It may not be reproduced, distributed, or altered in any fashion by any entity (either internal or external to VIPA), except in accordance with applicable agreements, contracts or licensing, without the express written consent of VIPA and the business management owner of the material.

For permission to reproduce or distribute, please contact: VIPA, Gesellschaft für Visualisierung und Prozessautomatisierung mbH Ohmstraße 4, D-91074 Herzogenaurach, Germany Tel.: +49 (91 32) 744 -0 Fax.: +49 9132 744 1864 EMail: info@vipa.de http://www.vipa.de

#### Note

Every effort has been made to ensure that the information contained in this document was complete and accurate at the time of publishing. Nevertheless, the authors retain the right to modify the information. This customer document describes all the hardware units and functions known at the present time. Descriptions may be included for units which are not present at the customer site. The exact scope of delivery is described in the respective purchase contract.

#### **CE Conformity**

Hereby, VIPA GmbH declares that the products and systems are in compliance with the essential requirements and other relevant provisions of the following directives:

- 2004/108/EC Electromagnetic Compatibility Directive

- 2006/95/EC Low Voltage Directive

Conformity is indicated by the CE marking affixed to the product.

#### **Conformity Information**

For more information regarding CE marking and Declaration of Conformity (DoC), please contact your local VIPA customer service organization.

#### Trademarks

VIPA, SLIO, System 100V, System 200V, System 300V, System 300S, System 400V, System 500S and Commander Compact are registered trademarks of VIPA Gesellschaft für Visualisierung und Prozessautomatisierung mbH.

SPEED7 is a registered trademark of profichip GmbH.

SIMATIC, STEP, SINEC, S7-300 and S7-400 are registered trademarks of Siemens AG.

Microsoft und Windows are registered trademarks of Microsoft Inc., USA.

Portable Document Format (PDF) and Postscript are registered trademarks of Adobe Systems, Inc.

All other trademarks, logos and service or product marks specified herein are owned by their respective companies.

#### Information product support

Contact your local VIPA Customer Service Organization representative if you wish to report errors or questions regarding the contents of this document. If you are unable to locate a customer service center, contact VIPA as follows:

VIPA GmbH, Ohmstraße 4, 91074 Herzogenaurach, Germany

Telefax:+49 9132 744 1204 EMail: documentation@vipa.de

#### **Technical support**

Contact your local VIPA Customer Service Organization representative if you encounter problems with the product or have questions regarding the product. If you are unable to locate a customer service center, contact VIPA as follows:

VIPA GmbH, Ohmstraße 4, 91074 Herzogenaurach, Germany

Telephone: +49 9132 744 1150 (Hotline) EMail: support@vipa.de

### Contents

|              | nanual                                            |      |

|--------------|---------------------------------------------------|------|

| •            | mation                                            |      |

|              | Basics                                            |      |

|              | rmation for Users                                 |      |

| •            | structure of a CPU                                |      |

|              | 2AG12                                             |      |

| -            | Assembly and installation guidelines              |      |

|              | dimensions                                        |      |

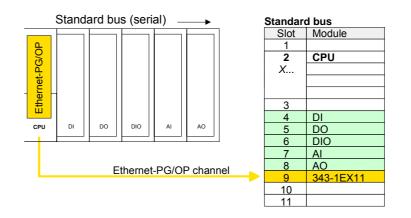

| •            | standard bus                                      |      |

| -            |                                                   |      |

| Installation | guidelines                                        | 2-6  |

| Chapter 3    | Hardware description                              | 3-1  |

| Properties   |                                                   | 3-2  |

| Structure    |                                                   | 3-3  |

| Technical I  | Data                                              | 3-8  |

| Chapter 4    | Deployment CPU 315-2AG12                          | 4-1  |

| Assembly.    |                                                   |      |

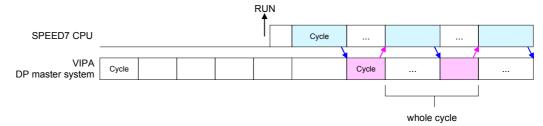

| Start-up be  | ehavior                                           |      |

| Addressing   | ]                                                 |      |

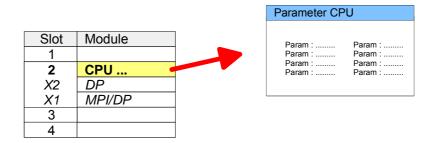

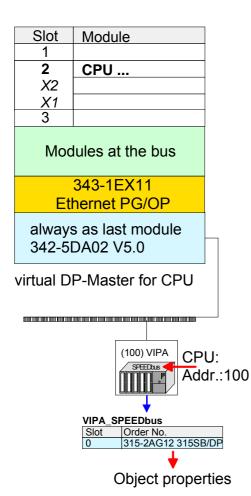

| Hardware     | configuration - CPU                               |      |

|              | configuration - I/O modules                       |      |

| Hardware     | configuration - Ethernet PG/OP channel            |      |

| Setting sta  | ndard CPU parameters                              |      |

| •            | PA specific CPU parameters                        |      |

| Project tra  | nsfer                                             | 4-21 |

| Access to    | the internal Web page                             | 4-25 |

| Operating    | modes                                             | 4-27 |

| Overall res  | et                                                | 4-30 |

| Firmware u   | update                                            | 4-32 |

| -            | set                                               |      |

|              | rage media                                        |      |

| Memory ex    | tension with MCC                                  | 4-37 |

| Extended I   | know-how protection                               | 4-38 |

| MMC-Cmd      | - Auto commands                                   |      |

| -            | ific diagnostic entries                           |      |

| Using test   | functions for control and monitoring of variables |      |

| Chapter 5    | Deployment PtP communication                      |      |

|              | uction                                            |      |

| •            | f the data transfer                               |      |

|              | nt of RS485 interface for PtP                     |      |

|              | ization                                           |      |

|              | ation                                             |      |

|              | and procedures                                    |      |

| Modbus - F   | Function codes                                    | 5-20 |

| Modbus - E   | Example communication                             | 5-24 |

| Chapter 6    | Deployment PROFIBUS communication | 6-1  |

|--------------|-----------------------------------|------|

| Overview     |                                   | 6-2  |

| Fast introd  | uction                            | 6-3  |

| Hardware     | configuration - CPU               | 6-4  |

| Deploymer    | nt as PROFIBUS DP master          | 6-5  |

| Deploymer    | nt as PROFIBUS DP slave           | 6-6  |

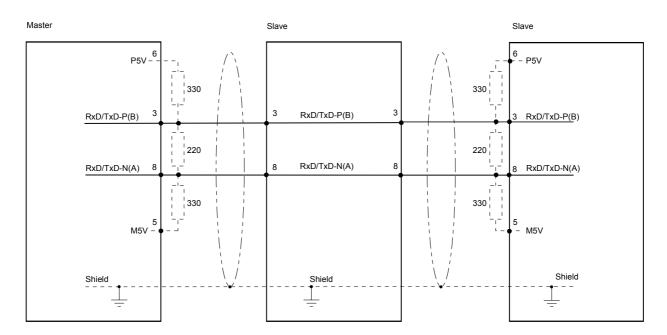

| PROFIBUS     | S installation guidelines         | 6-8  |

| Commissio    | oning and Start-up behavior       | 6-11 |

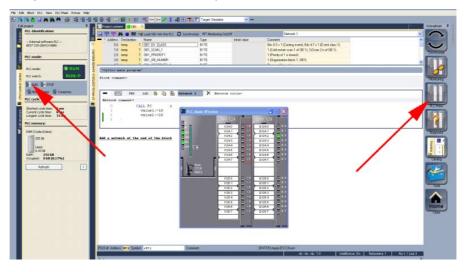

| Chapter 7    | WinPLC7                           | 7-1  |

| System pre   | esentation                        | 7-2  |

| Installation |                                   | 7-3  |

| Example p    | roject engineering                | 7-4  |

### About this manual

This manual describes the System 300S SPEED7 CPU 315-2AG12 from VIPA. Here you may find every information for commissioning and operation.

#### Overview Chapter 1: Basics

These basics contain hints for the usage and information about the project engineering of a SPEED7 system from VIPA.

General information about the System 300S like dimensions and environment conditions will also be found.

#### Chapter 2: Assembly and installation guidelines

In this chapter you will find every information, required for the installation and the cabling of a process control with the components of the System 300S with a CPU 315-2AG12.

#### Chapter 3: Hardware description

Here the hardware components of the CPU 315-2AG12 are described. The technical data are at the end of the chapter.

#### Chapter 4: Deployment CPU 315-2AG12

This chapter describes the deployment of a CPU 315-2AG12 with SPEED7 technology in the System 300S. The description refers directly to the CPU and to the deployment in connection with peripheral modules, mounted on a profile rail together with the CPU at the standard bus.

#### Chapter 5: Deployment PtP communication

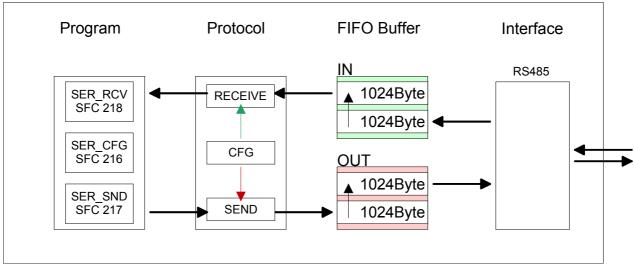

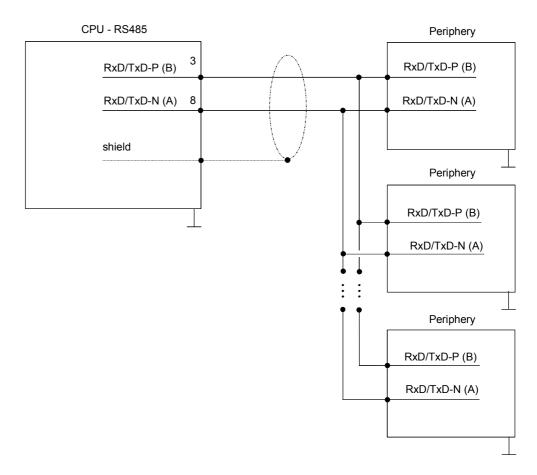

Content of this chapter is the deployment of the RS485 interface for serial PtP communication. Here you'll find every information about the protocols, the activation and project engineering of the interface, which are necessary for the serial communication using the RS485 interface.

#### Chapter 6: Deployment PROFIBUS communication

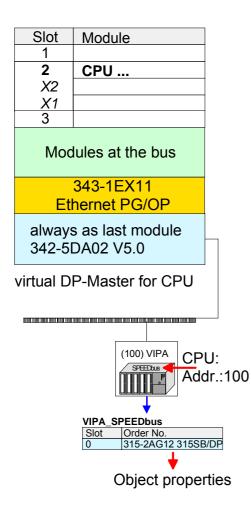

Content of this chapter is the deployment of the CPU 315-2AG12 with PROFIBUS. After a short overview the project engineering and parameterization of a CPU 315-2AG12 with integrated PROFIBUS-Part from VIPA is shown. Further you get information about usage as DP master and DP slave of the PROFIBUS part. The chapter is ending with notes to commissioning and start-up behavior.

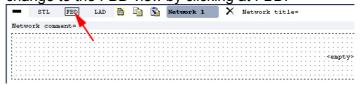

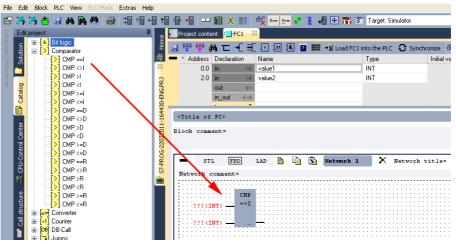

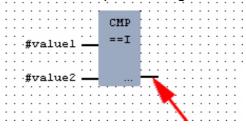

#### Chapter 7: WinPLC7

In this chapter the programming and simulation software WinPLC7 from VIPA is presented. WinPLC7 is suited for every with Siemens STEP<sup>®</sup>7 programmable PLC. Besides the system presentation and installation here the basics for using the software is explained with a sample project.

More information concerning the usage of WinPLC7 may be found in the online help respectively in the online documentation of WinPLC7.

**Objective and** This manual describes the System 300S SPEED7 CPU 315-2AG12 from VIPA. It contains a description of the construction, project implementation contents and usage. This manual is part of the documentation package with order number HB140E\_CPU and relevant for: Product Order number as of state: CPU-HW CPU-FW **DPM-FW** CPU 315SB/DPM VIPA 315-2AG12 V343 V312 01 **Target audience** The manual is targeted at users who have a background in automation technology. Structure of the The manual consists of chapters. Every chapter provides a self-contained description of a specific topic. manual Guide to the The following guides are available in the manual: document an overall table of contents at the beginning of the manual an overview of the topics for every chapter **Availability** The manual is available in: printed form, on paper • in electronic form as PDF-file (Adobe Acrobat Reader) Icons Important passages in the text are highlighted by following icons and headings: Headings Danger! Immediate or likely danger. Personal injury is possible. Attention! Damages to property is likely if these warnings are not heeded.

**Note!** Supplementary information and useful tips.

### **Safety information**

Applications conforming with specifications The SPEED7 CPU is constructed and produced for:

- all VIPA System 300S components

- communication and process control

- general control and automation applications

- industrial applications

- operation within the environmental conditions specified in the technical data

- installation into a cubicle

#### Danger!

This device is not certified for applications in

• in explosive environments (EX-zone)

Documentation

The manual must be available to all personnel in the

- project design department

- installation department

- commissioning

- operation

## The following conditions must be met before using or commissioning the components described in this manual:

- Hardware modifications to the process control system should only be carried out when the system has been disconnected from power!

- Installation and hardware modifications only by properly trained personnel.

- The national rules and regulations of the respective country must be satisfied (installation, safety, EMC ...)

Disposal Natio

National rules and regulations apply to the disposal of the unit!

### Chapter 1 Basics

OverviewThis Basics contain hints for the usage and information about the project<br/>engineering of a SPEED7 system from VIPA.General information about the System 300S like dimensions and

environment conditions will also be found.

Content Topic Page

| ontent | ropic                  |       | aye |

|--------|------------------------|-------|-----|

|        | Chapter 1 Basics       |       | 1-1 |

|        | •                      | Users |     |

|        | Operating structure of | a CPU | 1-3 |

|        | CPU 315-2AG12          |       | 1-6 |

### **Safety Information for Users**

Handling of electrostatic sensitive modules VIPA modules make use of highly integrated components in MOS-Technology. These components are extremely sensitive to over-voltages that can occur during electrostatic discharges.

The following symbol is attached to modules that can be destroyed by electrostatic discharges.

The Symbol is located on the module, the module rack or on packing material and it indicates the presence of electrostatic sensitive equipment.

It is possible that electrostatic sensitive equipment is destroyed by energies and voltages that are far less than the human threshold of perception. These voltages can occur where persons do not discharge themselves before handling electrostatic sensitive modules and they can damage components thereby, causing the module to become inoperable or unusable.

Modules that have been damaged by electrostatic discharges can fail after a temperature change, mechanical shock or changes in the electrical load.

Only the consequent implementation of protection devices and meticulous attention to the applicable rules and regulations for handling the respective equipment can prevent failures of electrostatic sensitive modules.

Modules must be shipped in the original packing material.

Shipping of electrostatic sensitive modules

Measurements and alterations on electrostatic sensitive modules When you are conducting measurements on electrostatic sensitive modules you should take the following precautions:

- Floating instruments must be discharged before use.

- Instruments must be grounded.

Modifying electrostatic sensitive modules you should only use soldering irons with grounded tips.

#### Attention!

Personnel and instruments should be grounded when working on electrostatic sensitive modules.

### **Operating structure of a CPU**

| General                      | The CPU contains a standard processor with internal program memory. In combination with the integrated SPEED7 technology the unit provides a powerful solution for process automation applications within the System 300S family.<br>A CPU supports the following modes of operation:                                                                                                      |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | cyclic operation                                                                                                                                                                                                                                                                                                                                                                           |

|                              | timer processing                                                                                                                                                                                                                                                                                                                                                                           |

|                              | alarm controlled operation                                                                                                                                                                                                                                                                                                                                                                 |

|                              | <ul> <li>priority based processing</li> </ul>                                                                                                                                                                                                                                                                                                                                              |

|                              |                                                                                                                                                                                                                                                                                                                                                                                            |

| Cyclic processing            | <b>Cyclic</b> processing represents the major portion of all the processes that are executed in the CPU. Identical sequences of operations are repeated in a never-ending cycle.                                                                                                                                                                                                           |

| Timer processing             | Where a process requires control signals at constant intervals you can initiate certain operations based upon a <b>timer</b> , e.g. not critical monitoring functions at one-second intervals.                                                                                                                                                                                             |

| Alarm controlled processing  | If a process signal requires a quick response you would allocate this signal to an <b>alarm controlled</b> procedure. An alarm can activate a procedure in your program.                                                                                                                                                                                                                   |

| Priority based<br>processing | The above processes are handled by the CPU in accordance with their <b>priority</b> . Since a timer or an alarm event requires a quick reaction, the CPU will interrupt the cyclic processing when these high-priority events occur to react to the event. Cyclic processing will resume, once the reaction has been processed. This means that cyclic processing has the lowest priority. |

| Applications                   | <ul><li>The program that is present in every CPU is divided as follows:</li><li>System routine</li><li>User application</li></ul>                                                                                                                                                                                                                                                                                                        |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System routine                 | The system routine organizes all those functions and procedures of the CPU that are not related to a specific control application.                                                                                                                                                                                                                                                                                                       |

| User application               | This consists of all the functions that are required for the processing of a specific control application. The operating modules provide the interfaces to the system routines.                                                                                                                                                                                                                                                          |

| Operands                       | <ul> <li>The following series of operands is available for programming the CPU:</li> <li>Process image and periphery</li> <li>Bit memory</li> <li>Timers and counters</li> <li>Data blocks</li> </ul>                                                                                                                                                                                                                                    |

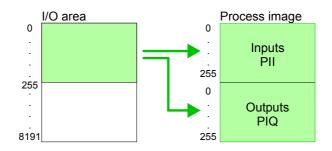

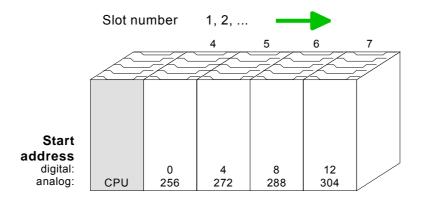

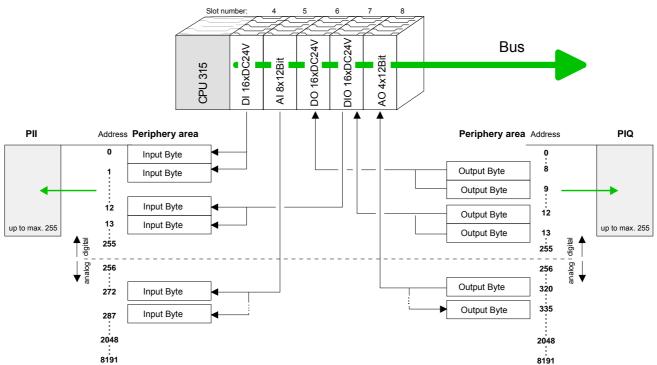

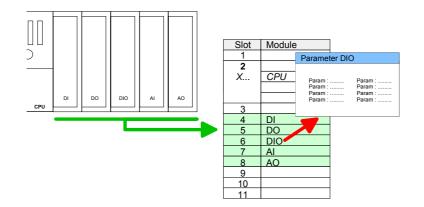

| Process image<br>and periphery | <ul> <li>The user application can quickly access the process image of the inputs and outputs PAA/PAE. You may manipulate the following types of data:</li> <li>individual Bits</li> <li>Bytes</li> <li>Words</li> <li>Double words</li> <li>You may also gain direct access to peripheral modules via the bus from user application. The following types of data are available:</li> <li>Bytes</li> <li>Words</li> <li>Blocks</li> </ul> |

**Bit Memory** The bit memory is an area of memory that is accessible by means of certain operations. Bit memory is intended to store frequently used working data.

You may access the following types of data:

- individual Bits

- Bytes

- Words

- Double words

#### **Timers and counters** In your program you may load cells of the timer with a value between 10ms and 9990s. As soon as the user application executes a start-operation, the value of this timer is decremented by the interval that you have specified until it reaches zero.

You may load counter cells with an initial value (max. 999) and increment or decrement these when required.

**Data Blocks** A data block contains constants or variables in the form of bytes, words or double words. You may always access the current data block by means of operands.

You may access the following types of data:

- individual Bits

- Bytes

- Words

- Double words

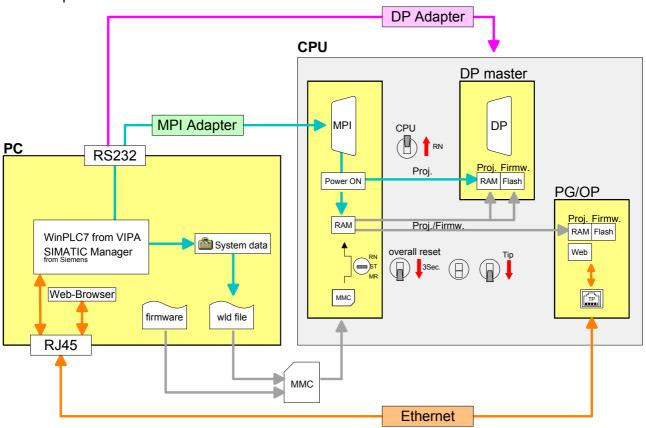

### CPU 315-2AG12

**Overview** The CPU 315-2AG12 bases upon the SPEED7 technology. This supports the CPU at programming and communication by means of co-processors that causes a power improvement for highest needs.

The SPEED7 CPUs from VIPA are instruction compatible to the programming language STEP<sup>®</sup>7 from Siemens and may be programmed via WinPLC7 from VIPA or via the Siemens SIMATIC Manager. Here the instruction set of the S7-400 from Siemens is used.

Modules and CPUs of the System 300S from VIPA and Siemens may be used at the bus as a mixed configuration.

The user application is stored in the battery buffered RAM or on an additionally pluggable MMC storage module.

The CPU is configured as CPU 318-2 (6ES7 318-2AJ00-0AB0/V3.0) from Siemens.

#### Access options

#### Note!

Please do always use the **CPU 318-2 (6ES7 318-2AJ00-0AB0/V3.0)** from Siemens of the hardware catalog to project this CPU from VIPA. For the project engineering, a thorough knowledge of the Siemens SIMATIC Manager and the hardware configurator from Siemens is required!

| Memory<br>management                    | <ul> <li>The CPU has an integrated memory. Information about the capacity (min. capacity max capacity) of the memory may be found at the front of the CPU. The memory is divided into the following 3 parts:</li> <li>Load memory 2Mbyte</li> <li>Code memory (50% of the work memory)</li> <li>Data memory (50% of the work memory)</li> <li>The work memory has 1Mbyte. There is the possibility to extend the work memory to its maximum printed capacity 2Mbyte by means of a MCC memory extension card.</li> </ul> |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

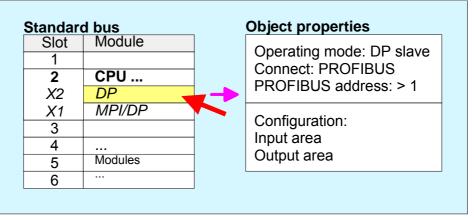

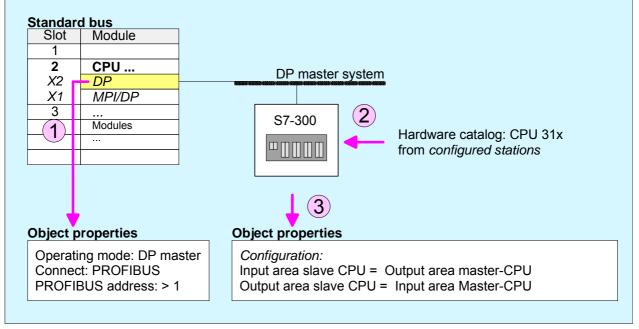

| Integrated<br>PROFIBUS<br>DP master     | The CPU has an integrated PROFIBUS DP master, which also may be<br>used as PROFIBUS DP salve.<br>The project engineering takes place or in the hardware configurator from<br>Siemens in WinPLC7 from VIPA.                                                                                                                                                                                                                                                                                                              |

| Integrated<br>Ethernet PG/OP<br>channel | The CPU has an Ethernet interface for PG/OP communication. Via the "PLC" functions you may directly access the Ethernet PG/OP channel and program res. remote control your CPU. A max. of 4 PG/OP connections is available.<br>You may also access the CPU with a visualization software via these connections.                                                                                                                                                                                                         |

| Operation Security                      | <ul> <li>Wiring by means of spring pressure connections (CageClamps) at the front connector</li> <li>Core cross-section 0.082.5mm<sup>2</sup></li> <li>Total isolation of the wiring at module change</li> <li>Potential separation of all modules to the backplane bus</li> <li>ESD/Burst acc. IEC 61000-4-2/IEC 61000-4-4 (up to level 3)</li> <li>Shock resistance acc. IEC 60068-2-6 / IEC 60068-2-27 (1G/12G)</li> </ul>                                                                                           |

| Environmental conditions                | <ul> <li>Operating temperature: 0 +60°C</li> <li>Storage temperature: -25 +70°C</li> <li>Relative humidity: 5 95% without condensation</li> <li>Ventilation by means of a fan is not required</li> </ul>                                                                                                                                                                                                                                                                                                                |

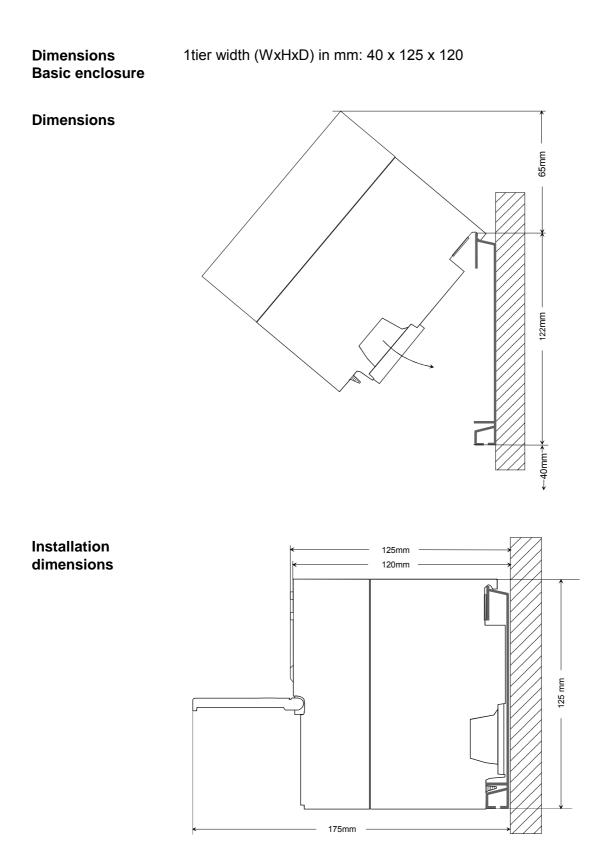

| Dimensions/<br>Weight                   | <ul> <li>Dimensions of the basic enclosure:<br/>1tier width: (WxHxD) in mm: 40x125x120</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Integrated<br>power supply              | The CPU comes with an integrated power supply. The power supply is to<br>be supplied with DC 24V. By means of the supply voltage, the internal<br>electronic is supplied as well as the connected modules via backplane bus.<br>The power supply is protected against inverse polarity and overcurrent.                                                                                                                                                                                                                 |

### Chapter 2 Assembly and installation guidelines

**Overview** In this chapter you will find every information, required for the installation and the cabling of a process control with the components of a CPU 315-2AG12 in the System 300S.

| Content | Торіс        |                                      | Page |

|---------|--------------|--------------------------------------|------|

|         | Chapter 2    | Assembly and installation guidelines | 2-1  |

|         | Installatior | n dimensions                         | 2-2  |

|         | Assembly     | standard bus                         | 2-3  |

|         | Cabling      |                                      | 2-5  |

|         | Installation | n guidelines                         | 2-6  |

### Installation dimensions

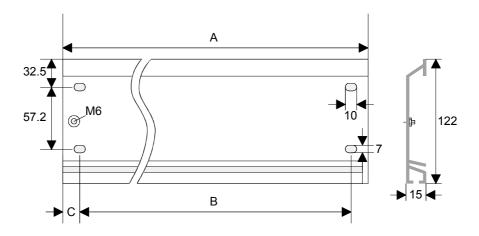

### Assembly standard bus

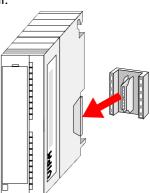

GeneralThe single modules are directly installed on a profile rail and connected via<br/>the backplane bus connector. Before installing the modules you have to<br/>clip the backplane bus connector to the module from the backside.<br/>The backplane bus connector is delivered together with the peripheral<br/>modules.

#### **Profile rail**

| Order number    | A    | В                   | С   |

|-----------------|------|---------------------|-----|

| VIPA 390-1AB60  | 160  | 140                 | 10  |

| VIPA 390-1AE80  | 482  | 466                 | 8.3 |

| VIPA 390-1AF30  | 530  | 500                 | 15  |

| VIPA 390-1AJ30  | 830  | 800                 | 15  |

| VIPA 390-9BC00* | 2000 | Drillings only left | 15  |

| *               |      |                     |     |

\* Unit pack: 10 pieces

Measures in mm

**Bus connector** For the communication between the modules the System 300S uses a backplane bus connector. Backplane bus connectors are included in the delivering of the peripheral modules and are clipped at the module from the backside before installing it to the profile rail.

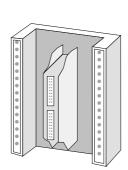

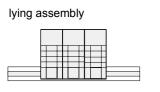

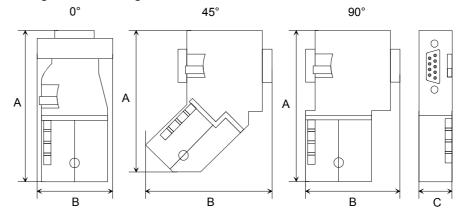

#### Assembly possibilities

©

horizontal assembly

Please regard the allowed environment temperatures:

- horizontal assembly:

- from 0 to 60°C vertical assembly:

- lying assembly:

- from 0 to 40°C from 0 to 40°C

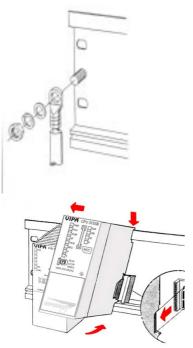

### Approach

- Bolt the profile rail with the background (screw size: M6), so that you still have minimum 65mm space above and 40mm below the profile rail.

- If the background is a grounded metal or device plate, please look for a low-impedance connection between profile rail and background.

- Connect the profile rail with the protected earth conductor. For this purpose there is a bolt with M6-thread.

- The minimum cross-section of the cable to the protected earth conductor has to be 10mm<sup>2</sup>.

- Stick the power supply to the profile rail and pull it to the left side to the grounding bolt of the profile rail.

- Fix the power supply by screwing.

- Take a backplane bus connector and click it at the CPU from the backside like shown in the picture.

- Stick the CPU to the profile rail right from the power supply and pull it to the power supply.

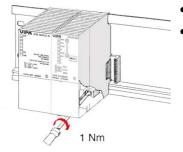

- Click the CPU downwards and bolt it like shown.

- Repeat this procedure with the peripheral modules, by clicking a backplane bus connector, stick the module right from the modules you've already fixed, click it downwards and connect it with the backplane bus connector of the last module and bolt it.

### Danger!

- The power supplies must be released before installation and repair • tasks, i.e. before handling with the power supply or with the cabling you must disconnect current/voltage (pull plug, at fixed connection switch off the concerning fuse)!

- Installation and modifications only by properly trained personnel!

### Cabling

(1)

#### Danger!

- The power supplies must be released before installation and repair tasks, i.e. before handling with the power supply or with the cabling you must disconnect current/voltage (pull plug, at fixed connection switch off the concerning fuse)!

- Installation and modifications only by properly trained personnel!

CageClamp technology (green) For the cabling of power supply of a CPU, a green plug with CageClamp technology is deployed.

The connection clamp is realized as plug that may be clipped off carefully if it is still cabled.

Here wires with a cross-section of  $0.08 \text{mm}^2$  to  $2.5 \text{mm}^2$  may be connected. You can use flexible wires without end case as well as stiff wires.

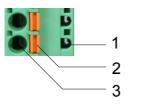

[1] Test point for 2mm test tip

[2] Locking (orange) for screwdriver

[3] Round opening for wires

The picture on the left side shows the cabling step by step from top view.

- For cabling you push the locking vertical to the inside with a suiting screwdriver and hold the screwdriver in this position.

- Insert the de-isolated wire into the round opening. You may use wires with a cross-section from 0.08mm<sup>2</sup> to 2.5mm<sup>2</sup>.

- By removing the screwdriver the wire is connected safely with the plug connector via a spring.

### Installation guidelines

| General                            | The installation guidelines contain information about the interference free deployment of System 300S systems. There is the description of the ways, interference may occur in your control, how you can make sure the electromagnetic digestibility (EMC), and how you manage the isolation.                                                                                                                                                                                                                                                               |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| What means<br>EMC?                 | Electromagnetic digestibility (EMC) means the ability of an electrical device, to function error free in an electromagnetic environment without being interferenced res. without interferencing the environment.<br>All System 300S components are developed for the deployment in hard industrial environments and fulfill high demands on the EMC. Nevertheless you should project an EMC planning before installing the components and take conceivable interference causes into account.                                                                |

| Possible<br>interference<br>causes | <ul> <li>Electromagnetic interferences may interfere your control via different ways:</li> <li>Fields</li> <li>I/O signal conductors</li> <li>Bus system</li> <li>Current supply</li> <li>Protected earth conductor</li> </ul> Depending on the spreading medium (lead bound or lead free) and the distance to the interference cause, interferences to your control occur by means of different coupling mechanisms. One differs: <ul> <li>galvanic coupling</li> <li>capacitive coupling</li> <li>inductive coupling</li> <li>radiant coupling</li> </ul> |

**Basic rules for** In the most times it is enough to take care of some elementary rules to guarantee the EMC. Please regard the following basic rules when installing your PLC.

- Take care of a correct area-wide grounding of the inactive metal parts when installing your components.

- Install a central connection between the ground and the protected earth conductor system.

- Connect all inactive metal extensive and impedance-low.

- Please try not to use aluminum parts. Aluminum is easily oxidizing and is therefore less suitable for grounding.

- When cabling, take care of the correct line routing.

- Organize your cabling in line groups (high voltage, current supply, signal and data lines).

- Always lay your high voltage lines and signal res. data lines in separate channels or bundles.

- Route the signal and data lines as near as possible beside ground areas (e.g. suspension bars, metal rails, tin cabinet).

- Proof the correct fixing of the lead isolation.

- Data lines must be laid isolated.

- Analog lines must be laid isolated. When transmitting signals with small amplitudes the one sided laying of the isolation may be favorable.

- Lay the line isolation extensively on an isolation/protected earth conductor rail directly after the cabinet entry and fix the isolation with cable clamps.

- Make sure that the isolation/protected earth conductor rail is connected impedance-low with the cabinet.

- Use metallic or metalized plug cases for isolated data lines.

- In special use cases you should appoint special EMC actions.

- Wire all inductivities with erase links.

- Please consider luminescent lamps can influence signal lines.

- Create a homogeneous reference potential and ground all electrical operating supplies when possible.

- Please take care for the targeted employment of the grounding actions. The grounding of the PLC is a protection and functionality activity.

- Connect installation parts and cabinets with the System 300S in star topology with the isolation/protected earth conductor system. So you avoid ground loops.

- If potential differences between installation parts and cabinets occur, lay sufficiently dimensioned potential compensation lines.

Isolation of<br/>conductorsElectrical, magnetically and electromagnetic interference fields are<br/>weakened by means of an isolation, one talks of absorption.

Via the isolation rail, that is connected conductive with the rack, interference currents are shunt via cable isolation to the ground. Hereby you have to make sure, that the connection to the protected earth conductor is impedance-low, because otherwise the interference currents may appear as interference cause.

When isolating cables you have to regard the following:

- If possible, use only cables with isolation tangle.

- The hiding power of the isolation should be higher than 80%.

- Normally you should always lay the isolation of cables on both sides. Only by means of the both-sided connection of the isolation you achieve high quality interference suppression in the higher frequency area.

Only as exception you may also lay the isolation one-sided. Then you only achieve the absorption of the lower frequencies. A one-sided isolation connection may be convenient, if:

- the conduction of a potential compensating line is not possible

- analog signals (some mV res. µA) are transferred

- foil isolations (static isolations) are used.

- With data lines always use metallic or metalized plugs for serial couplings. Fix the isolation of the data line at the plug rack. Do not lay the isolation on the PIN 1 of the plug bar!

- At stationary operation it is convenient to strip the insulated cable interruption free and lay it on the isolation/protected earth conductor line.

- To fix the isolation tangles use cable clamps out of metal. The clamps must clasp the isolation extensively and have well contact.

- Lay the isolation on an isolation rail directly after the entry of the cable in the cabinet. Lead the isolation further on to the System 300S module and **don't** lay it on there again!

#### Please regard at installation!

At potential differences between the grounding points, there may be a compensation current via the isolation connected at both sides. Remedy: Potential compensation line

### Chapter 3 Hardware description

**Overview** Here the hardware components of the CPU 315-2AG12 are described. The technical data are at the end of the chapter.

| Content | Торіс      |                      | Page |

|---------|------------|----------------------|------|

|         | Chapter 3  | Hardware description |      |

|         | Properties |                      |      |

|         | Structure. |                      |      |

|         | Technical  | Data                 |      |

### **Properties**

| <b>CPU 315SB/DPM</b><br>315-2AG12 | <ul> <li>SPEED7 technology integrated</li> <li>1Mbyte work memory integrated (512kbyte code, 512kbyte data)</li> <li>Memory expandable to max. 2Mbyte (1Mbyte code, 1MByte data)</li> <li>Load memory 2Mbyte</li> <li>PROFIBUS DP master integrated (DP-V0, DP-V1)</li> </ul> |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | <ul> <li>MPI interface</li> <li>MCC slot for external memory cards and memory extension</li> </ul>                                                                                                                                                                            |

- MCC slot for external memory cards and memory extension

- Status LEDs for operating state and diagnosis

- Real-time clock battery buffered

- Ethernet PG/OP interface integrated

- RS485 interface configurable for PROFIBUS DP master respectively PtP communication

- I/O address range digital/analog 8191byte

- 512 timer

- 512 counter

- 8192 flag byte

#### Ordering data

| Туре      | Order number   | Description                                                       |

|-----------|----------------|-------------------------------------------------------------------|

| 315SB/DPM | VIPA 315-2AG12 | MPI interface, card slot, real time clock, Ethernet interface for |

|           |                | PG/OP, PROFIBUS DP master                                         |

### Structure

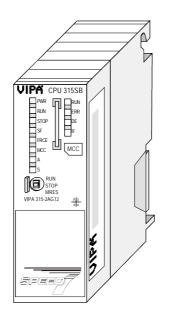

#### CPU 315SB/DPM 315-2AG12

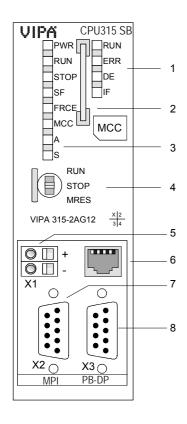

Interfaces

- [1] LEDs of the integrated **PROFIBUS DP master**

- [2] Storage media slot

- [3] LEDs of the CPU part

- Operating mode switch CPU [4]

#### The following components are under the front flap

- [5] Slot for DC 24V power supply

- Twisted pair interface [6]

- for Ethernet PG/OP channel

- [7] MPI interface

- [8] PROFIBUS DP/PtP interface

Transmit +

Transmit -

Receive +

Receive -

1 Ž

8 RxD/TxD-N (line A)

n.c.

Χ4

The CPU has an integrated power supply. The power supply has to be **Power supply** provided with DC 24V. For this serves the double DC 24V slot, that is X1 underneath the flap. Via the power supply not only the internal electronic is provided with voltage, but by means of the backplane bus also the connected modules. The power supply is protected against polarity inversion and overcurrent. The internal electronic is galvanically connected with the supply voltage. **MPI** interface 9-pin SubD jack: X2 The MPI interface serves for the connection between programming unit and CPU. By means of this the project engineering and programming happens. In addition MPI serves for communication between several CPUs or between HMIs and CPU. Standard setting is MPI Address 2. Ethernet PG/OP 8pin RJ45 jack: channel The RJ45 jack serves the interface to the Ethernet PG/OP channel. This X4 interface allows you to program res. remote control your CPU, to access the internal website or to connect a visualization. Configurable connections are not possible. For online access to the CPU via Ethernet PG/OP channel valid IP address parameters have to be assigned to this. More may be found at chapter "Deployment CPU ..." at "Initialization Ethernet PG/OP channel". PROFIBUS/PtP The CPU has a PROFIBUS/PtP interface with a fix pinout. After an overall reset the interface is deactivated. interface with configurable By appropriate configuration, the following functionalities for this interface functionality may be enabled: X3 PROFIBUS DP master operation PROFIBUS DP slave operation PtP functionality PROFIBUS The PROFIBUS master/slave functionality of this interface is activated by configuring the sub module X1 (MPI/DP) of the CPU in the hardware functionality configuration. PtP functionality Using the *PtP* functionality the RS485 interface is allowed to connect via serial point-to-point connection to different source res. target systems. Here the following protocols are supported: ASCII, STX/ETX, 3964R, USS and Modbus-Master (ASCII, RTU) . The activation of the PtP functionality happens by embedding the SPEEDBUS.GSD from VIPA in the hardware catalog. After the installation the CPU may be configured in a PROFIBUS master system and here the interface may be switched to PtP communication.

| Memory<br>management  | The CPU has an integrated memory. Information about the capacity (min. capacity max capacity) of the memory may be found at the front of the CPU.                                                                            |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                       | The memory is divided into the following 3 parts:                                                                                                                                                                            |  |  |  |

|                       | Load memory 2Mbyte                                                                                                                                                                                                           |  |  |  |

|                       | <ul> <li>Code memory (50% of the work memory)</li> </ul>                                                                                                                                                                     |  |  |  |

|                       | <ul> <li>Data memory (50% of the work memory)</li> </ul>                                                                                                                                                                     |  |  |  |

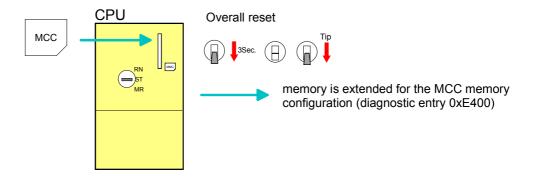

|                       | The work memory has 1Mbyte. There is the possibility to extend the work memory to its maximum printed capacity 2Mbyte by means of a MCC memory extension card.                                                               |  |  |  |

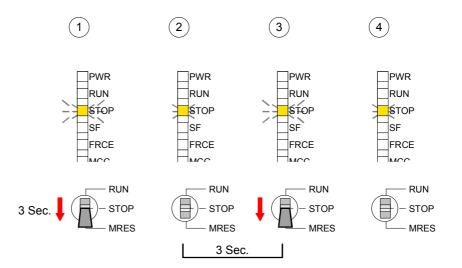

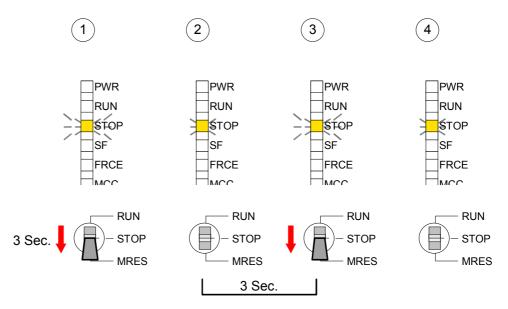

| Operating mode switch | With the operating mode switch you may switch the CPU between STOP and RUN.                                                                                                                                                  |  |  |  |

|                       | During the transition from STOP to RUN the operating mode START-UP is driven by the CPU.                                                                                                                                     |  |  |  |

| RUN<br>STOP<br>MRES   | Placing the switch to MRES (Memory Reset), you request an overall reset with following load from MMC, if a project there exists.                                                                                             |  |  |  |

|                       |                                                                                                                                                                                                                              |  |  |  |

| Storage<br>media slot | As external storage medium for applications and firmware you may use a MMC storage module ( <b>M</b> ultimedia <b>c</b> ard) or a MCC memory extension card. The MCC can additionally be used as an external storage medium. |  |  |  |

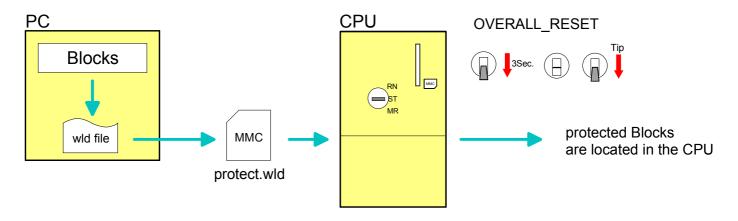

Both VIPA storage media are pre-formatted with the PC format FAT16 and can be accessed via a card reader. An access to the storage media always happens after an overall reset and PowerON.

After PowerON respectively an overall reset the CPU checks, if there is a storage medium with data valid for the CPU.

## **LEDs** The CPU has got LEDs on its front side. In the following the usage and the according colors of the LEDs is described.

**LEDs CPU** As soon as the CPU is supplied with 5V, the green PWR-LED is on.

| RUN<br>green                                   | STOP<br>yellow | SF<br>red | FRCE<br>yellow | MCC<br>yellow | Meaning                                                                                      |

|------------------------------------------------|----------------|-----------|----------------|---------------|----------------------------------------------------------------------------------------------|

| Boot-up after PowerON                          |                |           |                |               |                                                                                              |

| •                                              | Å <b>*</b>     | •         | •              | •             | * Blinking with 10Hz: Firmware is loaded.                                                    |

| •                                              | •              | •         | •              | •             | Initialization: Phase 1                                                                      |

| •                                              | •              | •         | •              | 0             | Initialization: Phase 2                                                                      |

| •                                              | •              | •         | 0              | 0             | Initialization: Phase 3                                                                      |

| 0                                              | •              | ٠         | 0              | 0             | Initialization: Phase 4                                                                      |

| Operatio                                       | on             |           |                |               |                                                                                              |

| 0                                              | •              | Х         | Х              | Х             | CPU is in STOP state.                                                                        |

| ¢                                              | 0              | Х         | х              | х             | CPU is in start-up state, the RUN LED blinks during operating OB100 at least for 3s.         |

| ●                                              | 0              | 0         | Х              | Х             | CPU is in state RUN without error.                                                           |

| Х                                              | Х              | •         | Х              | Х             | There is a system fault. More information may be found in the diagnostics buffer of the CPU. |

| Х                                              | Х              | Х         | •              | Х             | Variables are forced.                                                                        |

| Х                                              | Х              | Х         | Х              | •             | Access to the memory card.                                                                   |

| Overall                                        | reset          |           |                |               |                                                                                              |

| 0                                              | \<br>↓<br>↓    | Х         | X              | X             | Overall reset is requested.                                                                  |

| 0                                              | ☆*             | Х         | Х              | Х             | * Blinking with 5Hz: Overall reset is executed.                                              |

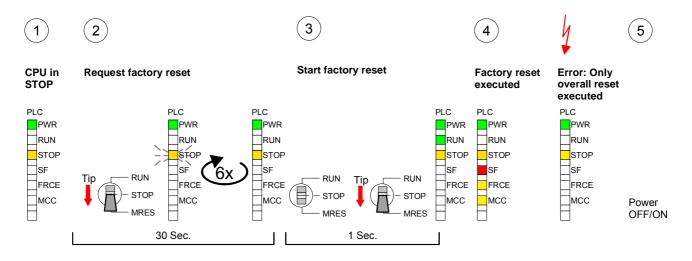

| Factory reset                                  |                |           |                |               |                                                                                              |

| •                                              | •              | 0         | 0              | 0             | Factory reset is executed.                                                                   |

| 0                                              | ●              | •         | •              | •             | Factory reset finished without error.                                                        |

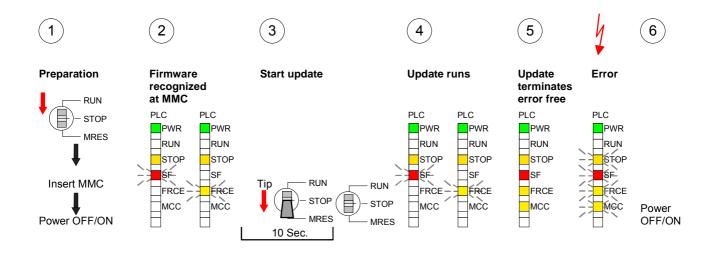

| Firmwar                                        | e update       |           |                | -             |                                                                                              |

| 0                                              | •              | ф         | Ф              | •             | The alternate blinking indicates that there is new firmware on the memory card.              |

| 0                                              | 0              | ф         | Ф              | •             | The alternate blinking indicates that a firmware update is executed.                         |

| 0                                              | ●              | ●         | •              | •             | Firmware update finished without error.                                                      |

| 0                                              | ☆*             | <b>☆*</b> | ☆*             | ☆*            | * Blinking with 10Hz: Error during Firmware update.                                          |

| on: ● off: ○ blinking (2Hz): ☆ not relevant: X |                |           |                |               |                                                                                              |

LEDs Ethernet PG/OP channel A, S The green A-LED (Activity) indicates the physical connection of the Ethernet PG/OP channel to Ethernet. Irregular flashing of the A-LED indicates communication of the Ethernet PG/OP channel via Ethernet.

If the green S-LED (Speed) is on, the Ethernet PG/OP has a communication speed of 100MBit/s otherwise with 10MBit/s.

#### LEDs PROFIBUS/PtP interface X3

Dependent on the mode of operation the LEDs show information about the state of operation of the PROFIBUS part according to the following pattern:

Master operation

| RUN   | ERR | DE    | IF  | Meaning                                                                                                        |

|-------|-----|-------|-----|----------------------------------------------------------------------------------------------------------------|

| green | red | green | red |                                                                                                                |

| 0     | 0   | 0     | 0   | Master has no project, this means the interface is deactivated respectively PtP is active.                     |

| •     | 0   | 0     | 0   | Master has bus parameters and is in RUN without slaves.                                                        |

| •     | 0   | ¢     | 0   | Master is in "clear" state (safety state). The inputs of the slaves may be read. The outputs are disabled.     |

| •     | 0   | •     | 0   | Master is in "operate" state, this means data exchange between master and slaves. The outputs may be accessed. |

| •     | •   | •     | 0   | CPU is in RUN, at least 1 slave is missing.                                                                    |

| •     | •   | ф.    | 0   | CPU is in STOP, at least 1 slave is missing.                                                                   |

| 0     | 0   | 0     | ٠   | Initialization error at faulty parameterization.                                                               |

| 0     | •   | 0     | •   | Waiting state for start command from CPU.                                                                      |

#### Slave operation

| RUN<br>green | ERR<br>red                                 | DE<br>green | IF<br>red | Meaning                                          |  |  |

|--------------|--------------------------------------------|-------------|-----------|--------------------------------------------------|--|--|

| 0            | 0                                          | 0           | 0         | Slave has no project respectively PtP is active. |  |  |

| ¢            | 0                                          | 0           | 0         | Slave is without master.                         |  |  |

| ☆*           | 0                                          | ☆*          | 0         | * Alternate flashing at configuration faults.    |  |  |

| •            | 0                                          | •           | 0         | Slave exchanges data between master.             |  |  |

| on: •        | ● off: ○ blinking (2Hz): ☆ not relevant: X |             |           |                                                  |  |  |

## **Technical Data**

| Order number                                                                                                                                                                                                                                                                                                                                                                                                                     | 315-2AG12                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Туре                                                                                                                                                                                                                                                                                                                                                                                                                             | CPU 315SB/DPM                                                                                         |

| SPEED-Bus                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                     |

| Technical data power supply                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| Power supply (rated value)                                                                                                                                                                                                                                                                                                                                                                                                       | DC 24 V                                                                                               |

| Power supply (permitted range)                                                                                                                                                                                                                                                                                                                                                                                                   | DC 20.428.8 V                                                                                         |

| Reverse polarity protection                                                                                                                                                                                                                                                                                                                                                                                                      | ✓                                                                                                     |

| Current consumption (no-load operation)                                                                                                                                                                                                                                                                                                                                                                                          | 200 mA                                                                                                |

| Current consumption (rated value)                                                                                                                                                                                                                                                                                                                                                                                                | 1 A                                                                                                   |

| Inrush current                                                                                                                                                                                                                                                                                                                                                                                                                   | 5 A                                                                                                   |

| Max. current drain at backplane bus                                                                                                                                                                                                                                                                                                                                                                                              | 2.5 A                                                                                                 |

| Load and working memory                                                                                                                                                                                                                                                                                                                                                                                                          | 2.5 A                                                                                                 |

| Load memory, integrated                                                                                                                                                                                                                                                                                                                                                                                                          | 2 MB                                                                                                  |

| Load memory, maximum                                                                                                                                                                                                                                                                                                                                                                                                             | 2 MB                                                                                                  |

| Work memory, integrated                                                                                                                                                                                                                                                                                                                                                                                                          | 1 MB                                                                                                  |

| Work memory, maximal                                                                                                                                                                                                                                                                                                                                                                                                             | 2 MB                                                                                                  |

| Memory divided in 50% program / 50% data                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                       |

| Memory card slot                                                                                                                                                                                                                                                                                                                                                                                                                 | MMC-Card with max. 1 GB                                                                               |

| Hardware configuration                                                                                                                                                                                                                                                                                                                                                                                                           | Minic-Card with max. 1 GB                                                                             |

| Racks, max.                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                                                                     |

| Modules per rack, max.                                                                                                                                                                                                                                                                                                                                                                                                           | 8 in multiple-, 32 in a single-                                                                       |

| Modules per rack, max.                                                                                                                                                                                                                                                                                                                                                                                                           | rack configuration                                                                                    |

| Number of integrated DP master                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| Number of DP master via CP                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                                     |

| Operable function modules                                                                                                                                                                                                                                                                                                                                                                                                        | 8                                                                                                     |

| Operable communication modules PtP                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                     |

| Operable communication modules LAN                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                     |

| Status information, alarms, diagnostics                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                     |

| Status mornation, alarms, diagnostics                                                                                                                                                                                                                                                                                                                                                                                            | 1/05                                                                                                  |

| Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                       | yes                                                                                                   |

| Process alarm                                                                                                                                                                                                                                                                                                                                                                                                                    | no                                                                                                    |

| Diagnostic interrupt                                                                                                                                                                                                                                                                                                                                                                                                             | no                                                                                                    |

| Command processing times                                                                                                                                                                                                                                                                                                                                                                                                         | no                                                                                                    |

| Bit instructions, min.                                                                                                                                                                                                                                                                                                                                                                                                           | 0.01.00                                                                                               |

| Word instruction, min.                                                                                                                                                                                                                                                                                                                                                                                                           | 0.01 μs<br>0.01 μs                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.01 us                                                                                               |

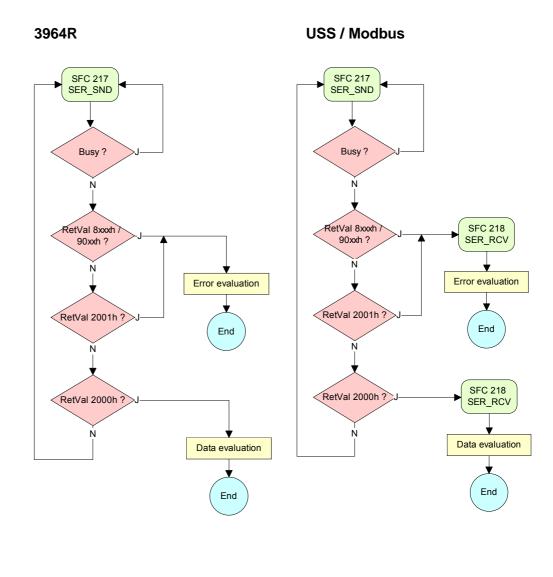

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |